## Spiking Neuron Processing Core (SNPC) Physical Design

**Technical Report**

© Adaptive Systems Laboratory

Division of Computer Engineering School of Computer Science and Engineering University of Aizu

> Contact: [d8211104, benab] @ u-aizu.ac.jp Edition: April 22, 2021

- 1. Specification and RTL design.

- 2. RTL Functional Simulation with Modelsim.

- 3. Synthesis with Cadence Genus.

- 4. Gate Level Simulation.

- 5. Place and Route with Cadence Innovus.

## Phase 1: Specification and RTL design

#### Contents

- Architecture

- Specification

- RTL Design

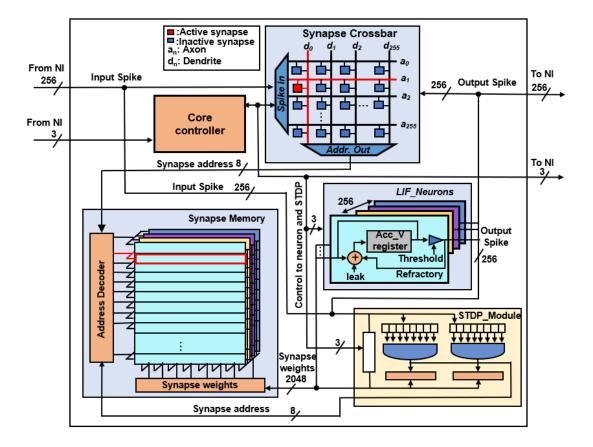

## High Level View of SNPC Architecture

## Specification and RTL Design

- First the logical behavior of the SNPC design is specified in Verilog HDL language. The logical behavior is described in the RTL level of abstraction, because it's most suitable for clocked designs. The SNPC design consist of sub-designs which are described in separate HDL codes. These sub designs are used in designs higher in hierarchy.

- Specification:

- 256 leaky integrate and fire (LIF) neurons

- 65K synapses: 256 SRAMs (256-bank, 8-bit)

- Spike timing-dependent plasticity (STDP) on-chip learning

- The design hierarchy of SNPC and the sub-designs is described below:

#### **SNPC**

-SNPC\_cntrl (core controller)

LIF\_neuron

Xbar (synapse crossbar, synapse memory)

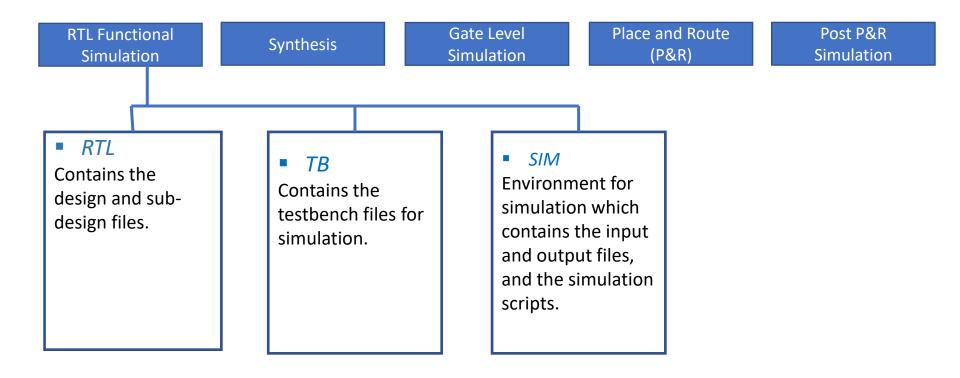

## Phase 2: RTL Functional Simulation with Modelsim

#### Contents

- RTL Functional simulation directory structure

- Environment setup

- Modelsim simulation and Result Verification

## **RTL Simulation with Modelsim**

- To test the logical behavior of the SNPC and the sub-designs, testbenches are specified. The testbenches are basically also a description in Verilog HDL which supplies the designs and sub-design with stimulus signals. The functional simulation is performed with interactive batch scripts. The SNPC design sources are first loaded in modelsim, and compiled starting from the top design, to the sub-designs, and then the testbench source. After compilation, the test bench is run, to perform the simulation (Both the compilation and simulation is performed using the interactive batch scripts). For this functional simulation, the MNIST dataset of 10,000 16×16 images are classified according to their labels from 1-9. The weights for this classification has been trained off-chip as ANN, and then converted to SNN. The MNIST images are converted to spikes using Poisson distribution.

- Specification:

- Network: 256:10 (single layer), 256:225:10 (2 layer)

- Synapses: 25,600, 59,850 (57,600 + 2250) 8-bit

- This simulation is going to be performed using batch scripts are in ~/SNPC/RTL\_SIM/script/ directory.

- The trained synapse weights are loaded into the synapse memory before simulation begins.

### **Directory Structure**

#### **Environment Setup**

|   | ikechukwu@zxp007:~/Documents/3D_NASH_FTKMCR/Tutorial/SNPC/SIM/work _             | ×  |

|---|----------------------------------------------------------------------------------|----|

|   | File Edit View Search Terminal Help                                              |    |

| 1 | [ikechukwu@zxp007 work]\$ source ~/.cad.sh<br>[ikechukwu@zxp007 work]\$ modelsim |    |

|   |                                                                                  |    |

|   |                                                                                  |    |

|   |                                                                                  |    |

|   |                                                                                  |    |

|   |                                                                                  | I. |

|   |                                                                                  |    |

|   |                                                                                  |    |

|   |                                                                                  |    |

|   |                                                                                  |    |

|   |                                                                                  |    |

(1) To set the functional simulator working environment, from the terminal, navigate to **~/SNPC/RTL\_SIM/work/**. If you are using file explorer, go to the same directory, right click and select **Open in Terminal**. Use the following commands to set the environment then launch modelsim.

> source ~/.cad.sh modelsim

#### **Begin RTL Simulation**

| ile <u>L'uit vien C</u> omplie | <u>a</u> muale | Add Transcript Tools Layout Bookmarks Window Help |   |

|--------------------------------|----------------|---------------------------------------------------|---|

|                                | 2              |                                                   |   |

| Layout NoDesign                |                | ColumnLayout AllColumns                           |   |

| 🗼 Library 🚃                    |                |                                                   | 6 |

| Name                           | Туре           | Path                                              |   |

| work                           | Library        | /home/ikechukwu/Documents/3D_NASH                 |   |

| 220model                       | Library        | \$MODEL_TECH//altera/vhdl/220model                |   |

| 220model_ver                   | Library        | \$MODEL_TECH//altera/verilog/220model             |   |

| altera                         | Library        | \$MODEL_TECH//altera/vhdl/altera                  |   |

| altera_Insim                   | Library        | \$MODEL_TECH//altera/vhdl/altera_Insim            |   |

| ···· altera_Insim_ver          | Library        | \$MODEL_TECH//altera/verilog/altera_I             |   |

| ···· altera_mf                 | Library        | \$MODEL_TECH//altera/vhdl/altera_mf               |   |

| mlis altera_mf_ver             | Library        | \$MODEL_TECH//altera/verilog/altera_mf            |   |

| ···· altera_ver                | Library        | \$MODEL_TECH//altera/verilog/altera               |   |

| ···· cyclone10gx               | Library        | \$MODEL_TECH//altera/vhdl/cyclone10               |   |

| … cyclone10gx_hip              | Library        | \$MODEL_TECH//altera/vhdl/cyclone10               |   |

| — cyclone10gx_hip_ve.          | . Library      | \$MODEL_TECH//altera/verilog/cyclone              |   |

| ം cyclone10gx_hssi             | Library        | \$MODEL_TECH//aitera/vhdl/cyclone10               |   |

| … cyclone10gx_hssi_v.          |                | \$MODEL_TECH//altera/verilog/cyclone              |   |

|                                | 1.5            |                                                   |   |

| Transcript                     |                |                                                   |   |

|                                |                |                                                   |   |

|                                | /t/run_L       | ocal_MNIST.tcl                                    |   |

| ModelSim≻do/scrip              |                |                                                   |   |

| ModelSim> do/scrip             |                |                                                   |   |

| ModelSim> do/scrip             |                |                                                   |   |

| ModelSim>do∕scriµ              |                |                                                   |   |

| ModelSim≻do/scrip              |                |                                                   |   |

| ModelSim> do∕scrip             |                |                                                   |   |

| ModelSim≻do/scrip              |                |                                                   |   |

| ModelSim> do∕scrip             |                |                                                   |   |

| ModelSim> do∕scrip             |                |                                                   |   |

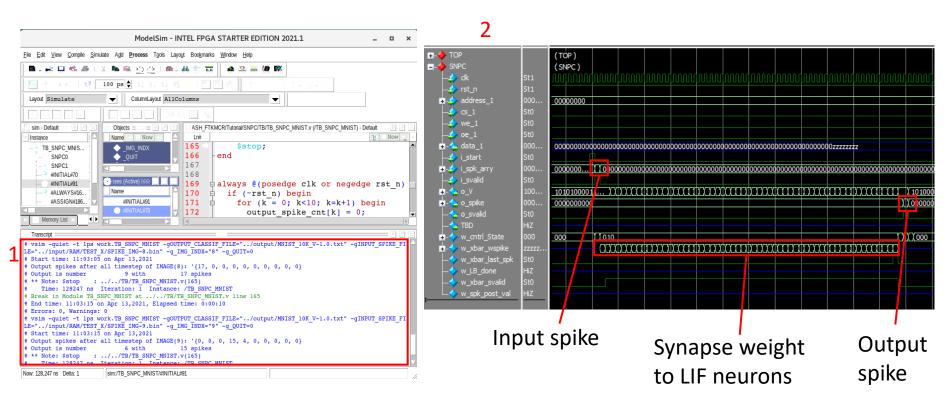

(1) After launching modelsim, use the following command to run the simulation. *do ../script/run\_Local\_MNIST.tcl*  Verification of RTL Simulation Results

(1) The simulation result is displayed in the modelsim transcript.

(2) Simulation waveform of the SNPC showing the input spikes, synapse weights sent to the LIF neurons and output spike.

## **Modify RTL Simulation Script**

set SRC\_DIR {../../RTL/}

```

if {[file isdirectory work]} {

# this is a directory

} else {

vlib work

vlog -quiet -vlog01compat -work work +incdir+$SRC_DIR ../../RTL/LIF neuron.v

vlog -guiet -vlog01compat -work work +incdir+$SRC DIR ../../RTL/xbar.v

#vlog -guiet -vlog01compat -work work +incdir+$SRC DIR .././RTL/LB.v

vlog -quiet -vlog01compat -work work +incdir+$SRC_DIR ../../RTL/aw ram dp sr sw.v

vlog -quiet -vlog01compat -work work +incdir+$SRC DIR ../../RTL/SNPC cntrl.v

vlog -quiet -vlog01compat -work work +incdir+$SRC DIR ../../RTL/SNPC.v

vlog -quiet -vlog01compat -work work +incdir+$SRC DIR ../../TB/TB SNPC MNIST.v

# vlog -vlog01compat -work work ../../TB/SNPC/TB SNPC MNIST 10K.v

}

for {set i 1} {$i < 10} {incr i} {</pre>

puts "I run the image

e: $i"

vsim -quiet -t lps -g QUIT=0 -g IMG INDX="$i" -gINPUT SPIKE FILE="../input/RAM/TEST X/SPIKE IMG-$i.bin" \

-aOUTPUT CLASSIF FILE="../output/MNIST 10K V-1.0.txt" work.TB SNPC MNIST

run -all

# quit -sim

add wave -group TOP /*

add wave -group TOP /output spike cnt

add wave -group SNPC0 /SNPC0/*

add wave -group SNPC1 /SNPC1/*

}

# quit -sim

exit

```

(1) Note: The MNIST simulation runs for 10 images by default. To change this number, open **~/SNPC/RTL\_SIM/script/ run\_Local\_MNIST.tcl** in text editor and the number of images can be changed to a maximum of 10,000. The simulation output is stored in **~/SNPC/RTL\_SIM/output**

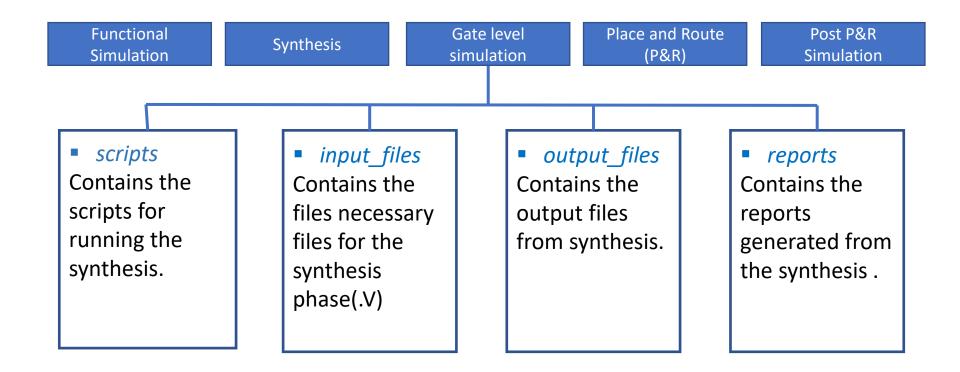

## Phase 3: Synthesis with Cadence Genus

#### Contents

- Synthesis directory structure

- Environment and Genus synthesis steps

- Synthesis generated files and reports

#### Synthesis directory structure

### Synthesis with Cadence Genus

- Now that the SNPC RTL design is logically valid, it should be synthesized into design which consists of only the standard cells and macros from the different libraries. For this, the single layer network and Cadence genus tool will be used. The synthesis is going to be done with a script. The script is written in TCL language, and specify the synthesis configuration, files, and constraints like clock period, input/output delay, library etc. The Nangate open cell library is used for this synthesis.

- The synthesis is going to be done in the ~/SNPC/SYNTH directory. From terminal, navigate to the ~/SNPC/SYNTH/ directory, or if you are using file explorer, go to the directory, right click and select Open in Terminal.

- The SNPC has 256 neurons. But to be able to perform gate level simulation and the post P&R simulation, we will synthesize for the single layer network with 10 neurons in the SNPC (Note: you can change the number of neurons in the SNPC to 256 before synthesis).

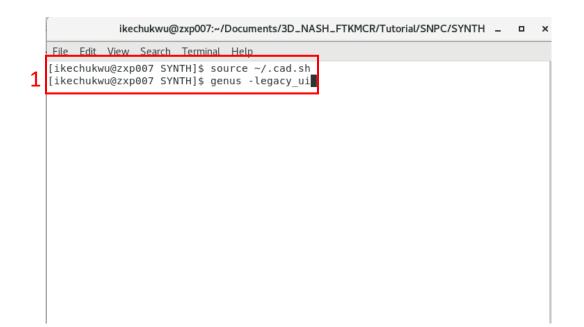

## Step 1: Environment and tool launch

(1) In terminal, type the following command to set the environment and launch Cadence genus:

source ~/.cad.sh genus -legacy\_ui

#### Synthesis Script

| ######################################                                                                                                                                                                                                                                                                                                                                                                                                | # Apply Constraints and generate clocks<br>set clock [define_clock -period \${myPeriod_ps} -name \${myClk} [clock_ports]]<br>external_delay -input \$myInDelay_ns -clock \${myClk} [find / -port ports_in/*]<br>external_delay -output \$myOutDelay_ns -clock \${myClk} [find / -port ports_out/*]                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre># Set the search paths to the libraries and the HDL files<br/># Remember that "." means your current directory. Add more directories<br/># after the . if you like.<br/>set_attribute hdl_search_path {./Src/}<br/>set_attribute lib_search_path {.//LIB/}<br/>set_attribute library [list typical.lib output_sp_w8_b256_freepdk45/sram_sp_w8_b256_freepdk45_TT_1p1V_25C.lib]<br/>set_attribute information_level 6</pre>        | <ul> <li># Sets transition to default values for Synopsys SDC format,</li> <li>#fall/rise 400ps</li> <li>dc::set_clock_transition .4 \$myClk</li> <li># check that the design is OK so far</li> <li>check_design -unresolved</li> <li>report timing -lint</li> </ul>                                                                                                                                                                                                                                                                             |

| <pre>set myFiles [list LIF.v LIF_neuron.v SNPC.v SNPC_cntrl.v xbar.v common.v ];# All HDL files set basename SNPC ;# name of top level module set myClk clk ;# clock name set myPeriod_ps 10000 ;# Clock period in ns set myInDelay_ns 0.1 ;# delay from clock to inputs valid set myOutDelay_ns 0.1 ;# delay from clock to output valid set runname net ;# name appended to output files #************************************</pre> | <pre># Synthesize the design to the target library synthesize -to_mapped # Write out the reports report timing &gt; ./reports/\${basename}_\${runname}_timing.rep report gates &gt; ./reports/\${basename}_\${runname}_cell.rep report power &gt; ./reports/\${basename}_\${runname}_power.rep report area &gt; ./reports/\${basename}_\${runname}_area.rep # Write out the structural Verilog and sdc files write_hdl -mapped &gt; ./output_files/\${basename}_\${runname}_sdc write_sdf &gt; ./output_files/\${basename}_\${runname}.sdf</pre> |

The synthesis script can be found in ~/SNPC/SYNTH/script/ directory. As shown in the image above, the design source and libraries are specified then the timing parameters are set before synthesis begins.

#### Step 2: Begin Synthesis

|   | File Edit View Search Terminal Help    |

|---|----------------------------------------|

| 1 | legacy_genus:/> source script/snpc.tcl |

|   |                                        |

|   |                                        |

|   |                                        |

|   |                                        |

(1) In terminal, to run the synthesis script, type the following command: source script/snpc.tcl

#### **Generated Files and Reports**

When the synthesis is done, the generated netlist and constraint files are saved in the *~SNPC/SYNTH/output\_files/* directory. The hardware complexity reports (area, cell, power, and timing) of both instances of SNPC are saved in the *~SNPC/SYNTH/reports/* directory.

#### Area Report

| Generated by: Genus(TM) Synthesis Solution 18.13-s027_1                                                |     |

|--------------------------------------------------------------------------------------------------------|-----|

| Generated on: Apr 19 2021 10:16:36 am                                                                  |     |

| Module: SNPC                                                                                           |     |

| Technology libraries: NangateOpenCellLibrary revision 1.0                                              |     |

| sram_sp_w8_b256_freepdk45_TT_1p1V_25C_lib                                                              |     |

| Operating conditions: typical (balanced_tree)                                                          |     |

| Wireload mode: enclosed                                                                                |     |

| Area mode: timing library                                                                              |     |

|                                                                                                        |     |

|                                                                                                        |     |

| Instance Module Cell Count Cell Area Net Area Total Area Wireload                                      |     |

|                                                                                                        |     |

| SNPC 3204 49002.671 0.000 49002.671 5K_hvratio_1_1 (D)                                                 |     |

| XBAR0 xbar_LAYER_INDX0_WEIGHT_WIDTH8_SPK_ARRAY_WIDTH256_ 2217 47267.553 0.000 47267.553 5K_hvratio_1_1 | (D) |

| LIF_GEN[9].LIF0 LIF_neuron_WEIGHT_WIDTH8_OUTPUT_REG0_26 97 170.772 0.000 170.772 5K_hvratio_1_1 (D)    |     |

| LIF_GEN[8].LIF0 LIF_neuron_WEIGHT_WIDTH8_OUTPUT_REG0_27 97 170.772 0.000 170.772 5K_hvratio_1_1 (D)    |     |

| LIF_GEN[7].LIF0 LIF_neuron_WEIGHT_WIDTH8_OUTPUT_REG0_28 97 170.772 0.000 170.772 5K_hvratio_1_1 (D)    |     |

| LIF_GEN[6].LIF0 LIF_neuron_WEIGHT_WIDTH8_OUTPUT_REG0_29 97 170.772 0.000 170.772 5K_hvratio_1_1 (D)    |     |

| LIF_GEN[5].LIF0 LIF_neuron_WEIGHT_WIDTH8_OUTPUT_REG0_30 97 170.772 0.000 170.772 5K_hvratio_1_1 (D)    |     |

| LIF_GEN[4].LIF0 LIF_neuron_WEIGHT_WIDTH8_OUTPUT_REG0_31 97 170.772 0.000 170.772 5K_hvratio_1_1 (D)    |     |

| LIF_GEN[3].LIF0 LIF_neuron_WEIGHT_WIDTH8_OUTPUT_REG0_32 97 170.772 0.000 170.772 5K_hvratio_1_1 (D)    |     |

| LIF_GEN[2].LIF0 LIF_neuron_WEIGHT_WIDTH8_OUTPUT_REG0_33 97 170.772 0.000 170.772 5K_hvratio_1_1 (D)    |     |

| LIF_GEN[1].LIF0 LIF_neuron_WEIGHT_WIDTH8_OUTPUT_REG0_34 97 170.772 0.000 170.772 5K_hvratio_1_1 (D)    |     |

| LIF_GEN[0].LIF0 LIF_neuron_WEIGHT_WIDTH8_OUTPUT_REG0 97 170.772 0.000 170.772 5K_hvratio_1_1 (D)       |     |

| CNTL0 SNPC_cntrl 15 25.802 0.000 25.802 5K_hvratio_1_1 (D)                                             |     |

|                                                                                                        |     |

| (D) = wireload is default in technology library                                                        |     |

The area report from synthesizing an SNPC with the single layer network is shown in the figure above describing the ten neurons, their synapse memory contained in the crossbar (xbar), and the control unit. The total area is depicted in 1

#### **Power Report**

Genus(TM) Synthesis Solution 18.13-s027\_1 Generated by: Apr 19 2021 10:16:36 am Generated on: Module: SNPC Technology libraries: NangateOpenCellLibrary revision 1.0 sram sp w8 b256 freepdk45 TT 1p1V 25C lib Operating conditions: typical (balanced\_tree) Wireload mode: enclosed Area mode: timing library Leakage Dynamic Total Cells Power(nW) Power(nW) Power(nW) Instance SNPC 3204 131531.155 2391192.834 2522723.989 XBAR0 2217 94371.775 1790324.843 1884696.617 LIF GEN[1].LIF0 97 3674.987 50217.790 53892.777 LIF\_GEN[3].LIF0 97 3670.734 59367.429 63038.163 97 3668.777 50887.476 54556.254 LIF\_GEN[6].LIF0 LIF\_GEN[5].LIF0 97 3663.160 52133.784 55796.944 LIF\_GEN[2].LIF0 97 3656.570 50652.893 54309.464 LIF GEN[9].LIF0 97 3653.810 52437.971 56091.781 LIF\_GEN[7].LIF0 97 3652.001 49376.049 53028.050 LIF GEN[4].LIF0 97 3651.879 54303.068 57954.948 LIF\_GEN[0].LIF0 97 3645.549 53134.886 56780.435 LIF GEN[8].LIF0 97 3644.805 50285.061 53929.866 CNTL0 15 543.179 9930.136 10473.315

The power report from synthesizing an SNPC with the single layer network is shown in the figure above describing the ten neurons, their synapse memory contained in the crossbar (xbar), and the control unit. The total power is depicted in 1

#### **Cell Report**

| Generated by: | Genus(TM) Synthesis Solution 18.13-s027_1   |

|---------------|---------------------------------------------|

| Generated on: |                                             |

| Module:       | SNPC                                        |

|               | raries: NangateOpenCellLibrary revision 1.0 |

|               | ram_sp_w8_b256_freepdk45_TT_1p1V_25C_lib    |

|               | ditions: typical (balanced_tree)            |

| Wireload mode |                                             |

| Area mode:    | timing library                              |

|               |                                             |

|               |                                             |

| Gate          | Instances Area Library                      |

| Gate          | Instances Area Library                      |

| AND2_X1       | 96 102.144 NangateOpenCellLibrary           |

| AND2_X4       | 1 2.394 NangateOpenCellLibrary              |

| AND3_X1       | 64 85.120 NangateOpenCellLibrary            |

| AND3_X4       | 1 2.926 NangateOpenCellLibrary              |

| AND4_X1       | 21 33.516 NangateOpenCellLibrary            |

| AOI211_X1     | 2 2.660 NangateOpenCellLibrary              |

| AOI21_X1      | 19 20.216 NangateOpenCellLibrary            |

| AOI221_X1     | 13 20.748 NangateOpenCellLibrary            |

| AOI222_X1     | 196 417.088 NangateOpenCellLibrary          |

| AOI22_X1      | 84 111.720 NangateOpenCellLibrary           |

| CLKBUF_X1     | 80 63.840 NangateOpenCellLibrary            |

| DFF_X1        | 389 1759.058 NangateOpenCellLibrary         |

| DFF_X2        | 1 5.054 NangateOpenCellLibrary              |

| FA_X1         | 70 297.920 NangateOpenCellLibrary           |

| INV_X1        | 545 289.940 NangateOpenCellLibrary          |

| INV_X16       | 1 4.522 NangateOpenCellLibrary              |

| INV_X8        | 2 4.788 NangateOpenCellLibrary              |

| MUX2_X1       | 10 18.620 NangateOpenCellLibrary            |

| NAND2_X1      | 189 150.822 NangateOpenCellLibrary          |

| NAND2_X4      | 1 2.394 NangateOpenCellLibrary              |

| NAND3_X1      | 57 60.648 NangateOpenCellLibrary            |

| NAND4_X1      | 51 67.830 NangateOpenCellLibrary            |

| NOR2_X1       | 217 173.166 NangateOpenCellLibrary          |

| NOR3_X1            | 108   | 114.912 NangateOpenCellLibrary                             |

|--------------------|-------|------------------------------------------------------------|

| NOR4_X1            | 170   | 226.100 NangateOpenCellLibrary                             |

| OAI211_X1          | 24    | 31.920 NangateOpenCellLibrary                              |

| OAI21_X1           | 136   | 144.704 NangateOpenCellLibrary                             |

| OAI21_X2           | 5     | 9.310 NangateOpenCellLibrary                               |

| OAI221_X1          | 103   | 3 164.388 NangateOpenCellLibrary                           |

| OAI222_X1          | 1     | 2.128 NangateOpenCellLibrary                               |

| OAI22_X1           | 25    | 33.250 NangateOpenCellLibrary                              |

| OR2_X1             | 46    | 48.944 NangateOpenCellLibrary                              |

| OR3_X1             | 43    | 57.190 NangateOpenCellLibrary                              |

| OR4_X1             | 79    | 126.084 NangateOpenCellLibrary                             |

| XNOR2_X1           | 139   | 9 221.844 NangateOpenCellLibrary                           |

| XOR2_X1            | 205   | 327.180 NangateOpenCellLibrary                             |

| sram_sp_w8_b256_fr | eepdk | k45 10 43797.583 sram_sp_w8_b256_freepdk45_TT_1p1V_25C_lib |

|                    |       |                                                            |

| total             | 32       | 204 49002.671                                                        |

|-------------------|----------|----------------------------------------------------------------------|

|                   | Library  | Instances Area Instances %                                           |

|                   |          | rary $31945205.088 99.7$<br>reepdk45_TT_1p1V_25C_lib 1043797.583 0.3 |

| sequen<br>inverte | -        |                                                                      |

| logic             | 2176 30  |                                                                      |

| total             | 3204 490 | 002.671 100.0                                                        |

The cell report provides a report of the number of instances and area of each of the library cell used for the design. 1 for the Nangate library and 2 for the SRAM library

#### **Timing Report**

|                                                                                                                                                                                                                                | M) Synthesis Solution 18.13-s027_1<br>021  10:16:36 am                                                                                                                                         | g3298/CO<br>g3296/CI                                                                                                                                             | FA_X1                                                                                    | 1 3.0 15 +72 5845 F<br>+19 5864                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Module: SNPC                                                                                                                                                                                                                   |                                                                                                                                                                                                | g3296/CO                                                                                                                                                         | FA_X1                                                                                    | 1 3.0 15 +72 5936 F                                                                                                              |

| Technology libraries: Nanga                                                                                                                                                                                                    | teOpenCellLibrary revision 1.0                                                                                                                                                                 | g3294/CI                                                                                                                                                         | <b>FA</b> 144                                                                            | +19 5955                                                                                                                         |

| sram_sp_w8_b2                                                                                                                                                                                                                  | 56_freepdk45_TT_1p1V_25C_lib                                                                                                                                                                   | g3294/CO                                                                                                                                                         | FA_X1                                                                                    | 5 9.5 24 +87 6042 F                                                                                                              |

| Operating conditions: typica                                                                                                                                                                                                   | II (balanced_tree)                                                                                                                                                                             | g3291/A                                                                                                                                                          | 04104 144                                                                                | +17 6059                                                                                                                         |

| Wireload mode: enclose                                                                                                                                                                                                         | d                                                                                                                                                                                              | g3291/ZN                                                                                                                                                         | OAI21_X1                                                                                 | 2 3.9 35 +33 6092 R                                                                                                              |

| Area mode: timing libr                                                                                                                                                                                                         | ary                                                                                                                                                                                            | g3284/C1                                                                                                                                                         | 0 4 10 4 4 V 4                                                                           | +13 6105                                                                                                                         |

|                                                                                                                                                                                                                                |                                                                                                                                                                                                | g3284/ZN                                                                                                                                                         | OAI211_X1                                                                                | 1 2.4 18 +28 6133 F                                                                                                              |

|                                                                                                                                                                                                                                |                                                                                                                                                                                                | g3277/A                                                                                                                                                          | VN0000 V4                                                                                | +15 6148                                                                                                                         |

| Pin Type                                                                                                                                                                                                                       | Fanout Load Slew Delay Arrival                                                                                                                                                                 | g3277/ZN                                                                                                                                                         | XNOR2_X1                                                                                 | 1 1.2 14 +41 6189 F                                                                                                              |

|                                                                                                                                                                                                                                | (fF) (ps) (ps) (ps)                                                                                                                                                                            | g3272/B                                                                                                                                                          |                                                                                          | +8 6197                                                                                                                          |

|                                                                                                                                                                                                                                |                                                                                                                                                                                                | g3272/Z                                                                                                                                                          | MUX2_X1                                                                                  | 3 5.4 14 +69 6265 F                                                                                                              |

| clock clk) launch                                                                                                                                                                                                              | 5000 F                                                                                                                                                                                         | g3269/A1                                                                                                                                                         |                                                                                          | +15 6281<br>2 4.0 15 +23 6304 R                                                                                                  |

| (BAR0                                                                                                                                                                                                                          |                                                                                                                                                                                                | g3269/ZN<br>g3265/A1                                                                                                                                             | NAND2_X1                                                                                 | 2 4.0 15 +23 6304 R<br>+14 6318                                                                                                  |

| GEN_RAM[9].R0/clk0                                                                                                                                                                                                             | 400 5000 F                                                                                                                                                                                     | g3265/ZN                                                                                                                                                         | NAND2_X1                                                                                 | 12 22.6 44 +58 6376 F                                                                                                            |

| GEN RAMIO R0/dout0171 (P)                                                                                                                                                                                                      |                                                                                                                                                                                                | 03203/ZIN                                                                                                                                                        | NAND2_A1                                                                                 | 12 22.0 44 TO 03/0F                                                                                                              |

| GEN_NAM[9].No/dout0[7](F)                                                                                                                                                                                                      | sram_sp_w8_b256_freepdk45                                                                                                                                                                      |                                                                                                                                                                  |                                                                                          | +00 6206                                                                                                                         |

|                                                                                                                                                                                                                                | +6 5311                                                                                                                                                                                        | g3263/A                                                                                                                                                          |                                                                                          | +20 6396                                                                                                                         |

| drc_buf_sp58949/A<br>drc_buf_sp58949/Z CLK                                                                                                                                                                                     |                                                                                                                                                                                                | g3263/A<br>g3263/ZN                                                                                                                                              | INV_X1                                                                                   | 1 1.9 14 +25 6421 R                                                                                                              |

| drc_buf_sp58949/A<br>drc_buf_sp58949/Z CLK<br>KBAR0/o_wspike[72]                                                                                                                                                               | +6 5311                                                                                                                                                                                        | g3263/A<br>g3263/ZN<br>g3261/C1                                                                                                                                  | -                                                                                        | 1 1.9 14 +25 6421 R<br>+11 6432                                                                                                  |

| drc_buf_sp58949/A<br>drc_buf_sp58949/Z CLK<br>(BAR0/o_wspike[72]<br>.IF_GEN[9].LIF0/i_wspike[0]                                                                                                                                | +6 <sup>5</sup> 5311<br>BUF_X1 3 5.1 15 +35 5347 F                                                                                                                                             | g3263/A<br>g3263/ZN<br>g3261/C1<br>g3261/ZN                                                                                                                      | INV_X1<br>A0I221_X1                                                                      | 1 1.9 14 +25 6421 R<br>+11 6432<br>1 1.8 22 +17 6449 F                                                                           |

| drc_buf_sp58949/A<br>drc_buf_sp58949/Z CLK<br>(BAR0/o_wspike[72]<br>.IF_GEN[9].LIF0/i_wspike[0]<br>g3323/A2                                                                                                                    | +6 <sup>5</sup> 5311<br>BUF_X1 3 5.1 15 +35 5347 F<br>+11 5358                                                                                                                                 | g3263/A<br>g3263/ZN<br>g3261/C1<br>g3261/ZN<br>g3254/A                                                                                                           | _<br>AOI221_X1                                                                           | 1 1.9 14 +25 6421 R<br>+11 6432<br>1 1.8 22 +17 6449 F<br>+12 6461                                                               |

| drc_buf_sp58949/A<br>drc_buf_sp58949/Z CLK<br>(BAR0/o_wspike[72]<br>.IF_GEN[9].LIF0/i_wspike[0]<br>g3323/A2<br>g3323/ZN AND2_X                                                                                                 | +6 5311<br>BUF_X1 3 5.1 15 +35 5347 F<br>+11 5358<br>I 1 3.0 7 +36 5394 F                                                                                                                      | g3263/A<br>g3263/ZN<br>g3261/C1<br>g3261/ZN<br>g3254/A<br>g3254/ZN                                                                                               | _<br>AOI221_X1<br>INV_X1                                                                 | 1 1.9 14 +25 6421 R<br>+11 6432<br>1 1.8 22 +17 6449 F<br>+12 6461<br>1 1.4 9 +17 6478 R                                         |

| drc_buf_sp58949/A<br>drc_buf_sp58949/Z CLK<br>(BAR0/o_wspike[72]<br>.IF_GEN[9].LIF0/i_wspike[0]<br>g3323/A2<br>g3323/ZN AND2_X <sup>-</sup><br>g3305/CI                                                                        | +6 5311<br>BUF_X1 3 5.1 15 +35 5347 F<br>+11 5358<br>1 1 3.0 7 +36 5394 F<br>+19 5412                                                                                                          | g3263/A<br>g3263/ZN<br>g3261/C1<br>g3261/ZN<br>g3254/A<br>g3254/ZN<br>r_acc_V_reg[1]/                                                                            | -<br>AOI221_X1<br>INV_X1<br>D <<< DFF_X1                                                 | 1 1.9 14 +25 6421 R<br>+11 6432<br>1 1.8 22 +17 6449 F<br>+12 6461<br>1 1.4 9 +17 6478 R<br>+9 <u>6487</u>                       |

| drc_buf_sp58949/A<br>drc_buf_sp58949/Z CLK<br>(BAR0/o_wspike[72]<br>.IF_GEN[9].LIF0/i_wspike[0]<br>g3323/A2<br>g3323/ZN AND2_X<br>g3305/CI<br>g3305/CO FA_X1                                                                   | +6 5311<br>BUF_X1 3 5.1 15 +35 5347 F<br>+11 5358<br>1 1 3.0 7 +36 5394 F<br>+19 5412<br>1 3.0 15 +69 5482 F                                                                                   | g3263/A<br>g3263/ZN<br>g3261/C1<br>g3261/ZN<br>g3254/A<br>g3254/ZN                                                                                               | -<br>AOI221_X1<br>INV_X1<br>D <<< DFF_X1                                                 | 1 1.9 14 +25 6421 R<br>+11 6432<br>1 1.8 22 +17 6449 F<br>+12 6461<br>1 1.4 9 +17 6478 R                                         |

| drc_buf_sp58949/A<br>drc_buf_sp58949/Z CLK<br>(BAR0/o_wspike[72]<br>.IF_GEN[9].LIF0/i_wspike[0]<br>g3323/A2<br>g3323/ZN AND2_X<br>g3305/CI<br>g3305/CO FA_X1<br>g3304/CI                                                       | +6 5311<br>BUF_X1 3 5.1 15 +35 5347 F<br>+11 5358<br>1 1 3.0 7 +36 5394 F<br>+19 5412<br>1 3.0 15 +69 5482 F<br>+19 5500                                                                       | g3263/A<br>g3263/ZN<br>g3261/C1<br>g3261/ZN<br>g3254/A<br>g3254/ZN<br>r_acc_V_reg[1]/<br>r_acc_V_reg[1]/                                                         | _<br>AOI221_X1<br>INV_X1<br>D <<< DFF_X1<br>CK setup                                     | 1 1.9 14 +25 6421 R<br>+11 6432<br>1 1.8 22 +17 6449 F<br>+12 6461<br>1 1.4 9 +17 6478 R<br>+9 6487<br>400 +56 6543 R            |

| drc_buf_sp58949/A<br>drc_buf_sp58949/Z CLK<br>(BAR0/o_wspike[72]<br>.IF_GEN[9].LIF0/i_wspike[0]<br>g3323/A2<br>g3323/ZN AND2_X<br>g3305/CI<br>g3305/CO FA_X1<br>g3304/CI<br>g3304/CO FA_X1                                     | +6 5311<br>BUF_X1 3 5.1 15 +35 5347 F<br>+11 5358<br>1 1 3.0 7 +36 5394 F<br>+19 5412<br>1 3.0 15 +69 5482 F<br>+19 5500<br>1 3.0 15 +72 5573 F                                                | g3263/A<br>g3263/ZN<br>g3261/C1<br>g3261/ZN<br>g3254/A<br>g3254/ZN<br>r_acc_V_reg[1]/                                                                            | -<br>AOI221_X1<br>INV_X1<br>D <<< DFF_X1                                                 | 1 1.9 14 +25 6421 R<br>+11 6432<br>1 1.8 22 +17 6449 F<br>+12 6461<br>1 1.4 9 +17 6478 R<br>+9 <u>6487</u>                       |

| drc_buf_sp58949/A<br>drc_buf_sp58949/Z CLK<br>(BAR0/o_wspike[72]<br>.IF_GEN[9].LIF0/i_wspike[0]<br>g3323/A2<br>g3323/ZN AND2_X<br>g3305/CI<br>g3305/CO FA_X1<br>g3304/CI<br>g3304/CO FA_X1<br>g3302/CI                         | +6 5311<br>BUF_X1 3 5.1 15 +35 5347 F<br>+11 5358<br>1 1 3.0 7 +36 5394 F<br>+19 5412<br>1 3.0 15 +69 5482 F<br>+19 5500<br>1 3.0 15 +72 5573 F<br>+19 5591                                    | g3263/A<br>g3263/ZN<br>g3261/C1<br>g3261/ZN<br>g3254/A<br>g3254/ZN<br>r_acc_V_reg[1]/<br>r_acc_V_reg[1]/<br>(clock clk)                                          | AOI221_X1<br>INV_X1<br>D <<< DFF_X1<br>CK setup<br>capture                               | 1 1.9 14 +25 6421 R<br>+11 6432<br>1 1.8 22 +17 6449 F<br>+12 6461<br>1 1.4 9 +17 6478 R<br>+9 6487<br>400 +56 6543 R            |

| drc_buf_sp58949/A<br>drc_buf_sp58949/Z CLK<br>(BAR0/o_wspike[72]<br>.IF_GEN[9].LIF0/i_wspike[0]<br>g3323/A2<br>g3323/ZN AND2_X<br>g3305/CI<br>g3305/CO FA_X1<br>g3304/CI<br>g3304/CO FA_X1<br>g3302/CI<br>g3302/CO FA_X1       | +6 5311<br>BUF_X1 3 5.1 15 +35 5347 F<br>+11 5358<br>1 1 3.0 7 +36 5394 F<br>+19 5412<br>1 3.0 15 +69 5482 F<br>+19 5500<br>1 3.0 15 +72 5573 F<br>+19 5591<br>1 3.0 15 +72 5664 F             | g3263/A<br>g3263/ZN<br>g3261/C1<br>g3261/ZN<br>g3254/A<br>g3254/ZN<br>r_acc_V_reg[1]/<br>r_acc_V_reg[1]/<br>clock clk)<br>                                       | AOI221_X1<br>INV_X1<br>D <<< DFF_X1<br>CK setup<br>capture<br>457ps                      | 1 1.9 14 +25 6421 R<br>+11 6432<br>1 1.8 22 +17 6449 F<br>+12 6461<br>1 1.4 9 +17 6478 R<br>+9 6487<br>400 +56 6543 R            |

| drc_buf_sp58949/A<br>drc_buf_sp58949/Z CLK<br>(BAR0/o_wspike[72]<br>.IF_GEN[9].LIF0/i_wspike[0]<br>g3323/A2<br>g3323/ZN AND2_X<br>g3305/Cl<br>g3305/CO FA_X1<br>g3304/Cl<br>g3302/Cl<br>g3302/Cl<br>g3302/CO FA_X1<br>g3300/Cl | +6 5311<br>BUF_X1 3 5.1 15 +35 5347 F<br>+11 5358<br>1 1 3.0 7 +36 5394 F<br>+19 5412<br>1 3.0 15 +69 5482 F<br>+19 5500<br>1 3.0 15 +72 5573 F<br>+19 5591<br>1 3.0 15 +72 5664 F<br>+19 5682 | g3263/A<br>g3263/ZN<br>g3261/C1<br>g3261/ZN<br>g3254/A<br>g3254/ZN<br>r_acc_V_reg[1]/<br>r_acc_V_reg[1]/<br>(clock clk)<br>Timing slack : 3<br>Start-point : XBA | _<br>AOI221_X1<br>D <<< DFF_X1<br>CK setup<br><br>capture<br>457ps<br>R0/GEN_RAM[9].R0/o | 1 1.9 14 +25 6421 R<br>+11 6432<br>1 1.8 22 +17 6449 F<br>+12 6461<br>1 1.4 9 +17 6478 R<br>+9 6487<br>400 +56 6543 R<br>10000 R |

| drc_buf_sp58949/A<br>drc_buf_sp58949/Z CLK<br>(BAR0/o_wspike[72]<br>IF_GEN[9].LIF0/i_wspike[0]<br>g3323/A2<br>g3323/ZN AND2_X<br>g3305/CI<br>g3305/CO FA_X1<br>g3304/CI<br>g3304/CO FA_X1<br>g3302/CI<br>g3302/CO FA_X1        | +6 5311<br>BUF_X1 3 5.1 15 +35 5347 F<br>+11 5358<br>1 1 3.0 7 +36 5394 F<br>+19 5412<br>1 3.0 15 +69 5482 F<br>+19 5500<br>1 3.0 15 +72 5573 F<br>+19 5591<br>1 3.0 15 +72 5664 F             | g3263/A<br>g3263/ZN<br>g3261/C1<br>g3261/ZN<br>g3254/A<br>g3254/ZN<br>r_acc_V_reg[1]/<br>r_acc_V_reg[1]/<br>(clock clk)<br>Timing slack : 3<br>Start-point : XBA | AOI221_X1<br>INV_X1<br>D <<< DFF_X1<br>CK setup<br>capture<br>457ps                      | 1 1.9 14 +25 6421 R<br>+11 6432<br>1 1.8 22 +17 6449 F<br>+12 6461<br>1 1.4 9 +17 6478 R<br>+9 6487<br>400 +56 6543 R<br>10000 R |

The timing report provides a report of the validation of timing performance of the SNPC. This validation is done by checking all possible paths for timing violations. 1 shows the period of the SNPC.

## Phase 4: Gate Level Simulation with Modelsim

#### Contents

- Gate level simulation directory structure

- Environment and Modelsim simulation

# Gate Level Simulation with Modelsim

- This is basically the same step as RTL simulation, only here the synthesized SNPC source is simulated together with a SDF (standard delay format) file. The synthesized SNPC source (netlist) is a structural description of the design, with all the standard cells and macro's (memory blocks) connected to each other in the best possible way, for a functional and fastest design. The SDF file contains of delay values for the used standard cells, and the interconnect delays are guessed, because Design Compiler doesn't contain any interconnect information. These delay values are annotated into the synthesized design and simulated.

- For this simulation, the same setup and MNIST dataset for RTL functional simulation is used.

#### **Environment setup**

|   | File Edit View Search Terminal Help                                              |

|---|----------------------------------------------------------------------------------|

| 1 | [ikechukwu@zxp007 work]\$ source ~/.cad.sh<br>[ikechukwu@zxp007 work]\$ modelsim |

|   |                                                                                  |

|   |                                                                                  |

|   |                                                                                  |

|   |                                                                                  |

|   |                                                                                  |

|   |                                                                                  |

|   |                                                                                  |

|   |                                                                                  |

|   |                                                                                  |

(1) To set the functional simulator working environment, from the terminal, navigate to **~/SNPC/GL\_SIM/work/**. If you are using file explorer, go to the same directory, right click and select **Open in Terminal**. Use the following command to set the environment and launch modelsim.

> source ~/.cad.sh modelsim"

#### **Begin Gate Level Simulation**

| 희 ~ 2       | 3 11 - 4         |         | <u>*2</u> :      | <u>`</u>               | 80 M  | 0 10 i |   |   |     |

|-------------|------------------|---------|------------------|------------------------|-------|--------|---|---|-----|

| Layout 1    | NoDesign         |         | ColumnLa         | ayout AllColum         | ns    |        | • | 1 |     |

| 📜 Library   |                  |         |                  |                        |       | 8      |   |   |     |

| Name        |                  | Туре    | Path             |                        |       |        |   |   |     |

| wor         | rk               | Library | /home/ikechukwu/ | Documents/3D_NA        | SH    |        |   |   |     |

| 220         | Omodel           | Library | \$MODEL_TECH/    | /altera/vhdl/220mo     | del   |        |   |   |     |

| 220         | Omodel_ver       | Library | \$MODEL_TECH/    | /altera/verilog/220n   | nodel |        |   |   |     |

| ··· alte    | era              | Library | \$MODEL_TECH/    | /altera/vhdl/altera    |       |        |   |   |     |

| ··· alte    | era_Insim        | Library | \$MODEL_TECH/    | /altera/vhdl/altera_l  | Insim |        |   |   |     |

| ···· alte   | era_Insim_ver    | Library | \$MODEL_TECH/    | /altera/verilog/altera | a_l   |        |   |   |     |

|             | era_mf           | Library | _                | /altera/vhdl/altera_   |       |        |   |   |     |

| .err¶⊿ alte |                  | Library | _                | /altera/verilog/altera | -     |        |   |   |     |

|             | -                | Library | _                | /altera/verilog/altera |       |        |   |   |     |

|             |                  | Library | -                | /altera/vhdl/cyclone   |       |        |   |   |     |

|             | clone10gx_hip    | Library | _                | /altera/vhdl/cyclone   |       |        |   |   |     |

|             | clone10gx_hip_ve | -       | -                | /altera/verilog/cyclo  |       |        |   |   |     |

|             | • <u>-</u>       | Library | -                | /altera/vhdl/cyclone   |       |        |   |   |     |

| сус         | clone10gx_hssi_v | Library | \$MODEL_TECH/    | /altera/verilog/cyclo  | one   |        |   |   |     |

| Transcri    | ipt 🖂            |         |                  |                        |       |        |   |   | = 1 |

|             |                  |         |                  |                        |       |        |   |   |     |

|             | do/scrip         | t/run_L | ocal_MNIST.      | tcl                    |       |        |   |   |     |

| ModelSim>   |                  |         |                  |                        |       |        |   |   |     |

| ModelSim>   |                  |         |                  |                        |       |        |   |   |     |

| ModelSim>   |                  |         |                  |                        |       |        |   |   |     |

| ModelSim>   |                  |         |                  |                        |       |        |   |   |     |

| ModelSim>   |                  |         |                  |                        |       |        |   |   |     |

| ModelSim>   |                  |         |                  |                        |       |        |   |   |     |

| ModelSim>   |                  |         |                  |                        |       |        |   |   |     |

| ModelSim>   |                  |         |                  |                        |       |        |   |   |     |

| ModelSim>   |                  |         |                  |                        |       |        |   |   |     |

(1) After launching modelsim, use the following command to run the simulation. *do ../script/run\_Local\_MNIST.tcl*

### **Modify Gate Level Simulation Script**

```

set SRC DIR {..//Netlist/}

#set LIB DIR {../../LIB/}

if {[file isdirectory work]} {

# this is a directory

} else {

vlib work

vlog -quiet -vlog01compat -work work +incdir+$SRC DIR ../Netlist/SNPC net.v

vlog -quiet -vlog01compat -work work +incdir+$SRC DIR ../../LIB/NangateOpenCellLibrary.v

vlog -quiet -vlog01compat -work work +incdir+$SRC DIR ../TB/TB SNPC MNIST.v

# vlog -vlog01compat -work work ../../TB/SNPC/TB SNPC MNIST 10K.v

}

for {set i 1} {$i

k 2} {incr i} {

puts "I run the image: $i'

vsim -quiet -t lps -g QUIT=0 -g IMG INDX="$i" -gINPUT SPIKE FILE="../input/RAM/TEST X/SPIKE IMG-$i.bin" \

-qOUTPUT CLASSIF FILE="../output/MNIST 10K V-1.0.txt" work.TB SNPC MNIST

run -all

#auit -sim

#add wave -group TOP /*

#add wave -group TOP /output spike cnt

#add wave -group SNPC0 /SNPC0/*

#add wave -group SNPC1 /SNPC1/*

}

# quit -sim

exit

```

(1) Note: The MNIST simulation runs for 2 images by default. To change this number, open ~/SNPC/GL\_SIM/script/ run\_Local\_MNIST.tcl in text editor and the number of images can be changed to a maximum of 10,000. The simulation output is stored in ~/SNPC/GL\_SIM/output

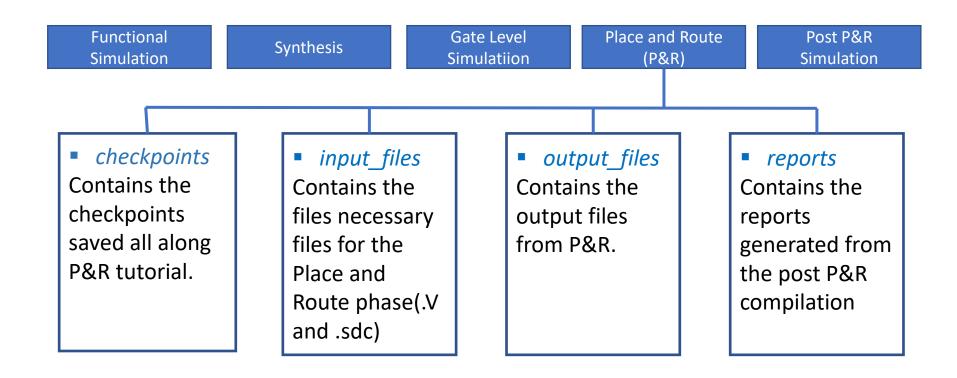

## Phase 5: Place & Route with Cadence Innovus

#### Contents

- Place & Route (P&R) directory structure

- Environment

- Innovus P&R steps (Batch mode)

- Innovus P&R steps (GUI mode)

#### Place and Route

- The place and route process places each macro from the synthesis netlist into an available location on the target silicon and connects the macros using routing resources available on the target silicon and technology. The place and route tools read the netlist, extract the components and nets from the netlist, place the components on the target device, and interconnect the components using the specified interconnections.

- To perform the place and route, copy the files generated from the netlist from ~/SNPC/SYNTH/RTL\_SYNTH/output\_files/ to ~/SNPC/PnR/input\_files/. The scripts for the place and place and route scripts are located in the /SNPC/PnR/scripts/ directory. Two of the scripts ".global" and ".view" are used to set the parameters (libraries, constraints, netlist) and conditions for the place and route. The next five scripts which their names begin with indexes from 0 to 5 are all scripts for various stage of the place and route stages: initialize, floor plan, place macro, place standard cell, route, and finish. The final script without index is used to call the other scripts during the place and route.

### Place & Route (Batch Mode) (1/3)

ikechukwu@zxp007:~/Documents/3D\_N/

| File | Edit | View | Search | Terminal | Help |  |

|------|------|------|--------|----------|------|--|

|      |      |      |        |          |      |  |

1 [ikechukwu@zxp007 PnR]\$ source ~/.cad.sh [ikechukwu@zxp007 PnR]\$ innovus

(1) To begin the place and route, navigate to ~/SNPC/PnR/ on terminal and type the following commands to setup the environment and launch the innovus tool:

source ~/.cad.sh innovus

ikechukwu@zxp007:~/Documents/3D\_NASH\_FTKMCR/Tu

File Edit View Search Terminal Help

innovus 3> source scripts/SNPC.tcl

(1) After the innovus tool has been launched the graphical user interface will also be launched. However, type the following command on the terminal to launch the place and route script. *source scripts/SNPC.tcl*

Note: The place and route will take some time to complete because the design is somewhat large.

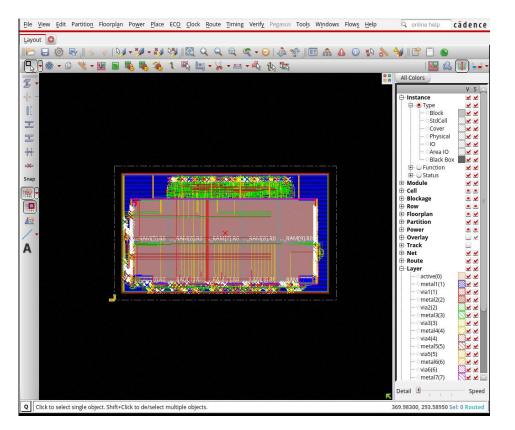

# Place & Route (Batch Mode) (3/3)

(1) The image above is the output of the place and route, along with other outputs and reports in the **~/SNPC/P&R/output\_files/** and **~/SNPC/P&R/reports/** directories respectively.

1

### Place & Route (GUI Mode)

| File         | Edit           | View             | Sea        | rch        | Ter          | rminal        | Help          |        |

|--------------|----------------|------------------|------------|------------|--------------|---------------|---------------|--------|

| [ike<br>[ike | chukw<br>chukw | /u@zxp<br>/u@zxp | 007<br>007 | PnR<br>PnR | 2]\$<br>2]\$ | sour<br>innov | ce ~/.<br>/us | cad.sh |

(1) To begin the place and route, navigate to ~/SNPC/PnR/ on terminal and type the following commands to setup the environment and launch the innovus tool:

source ~/.cad.sh innovus

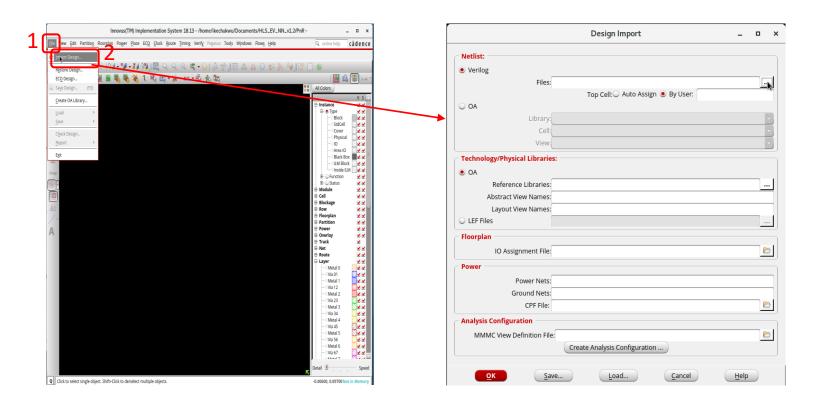

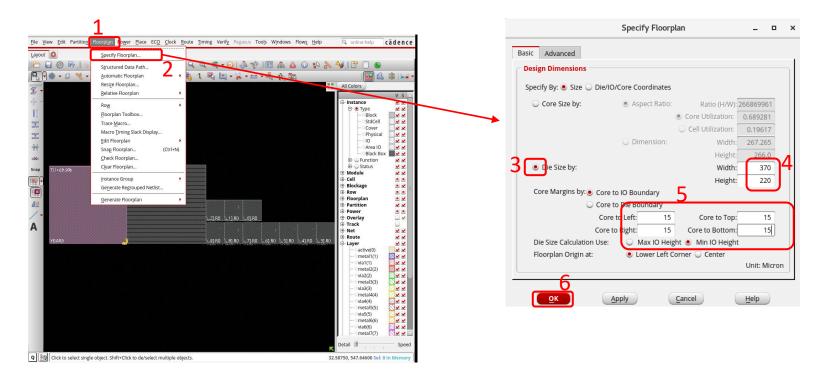

#### Step 1: Import Design

#### (1) Click on File -> (2) Import Design

#### Import design- Netlist File

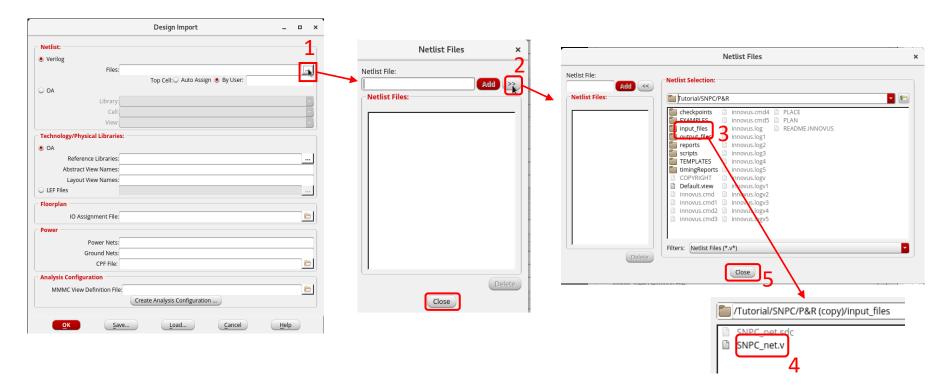

(1) Click **Files** to import the netlist. (2) Click on >> to expand. (3) Go to **./input\_files** folder. (4) Double click on **SNPC\_net.v**. (5) Click **Close** until you get to **Design import** window.

#### Import design- LEF Files

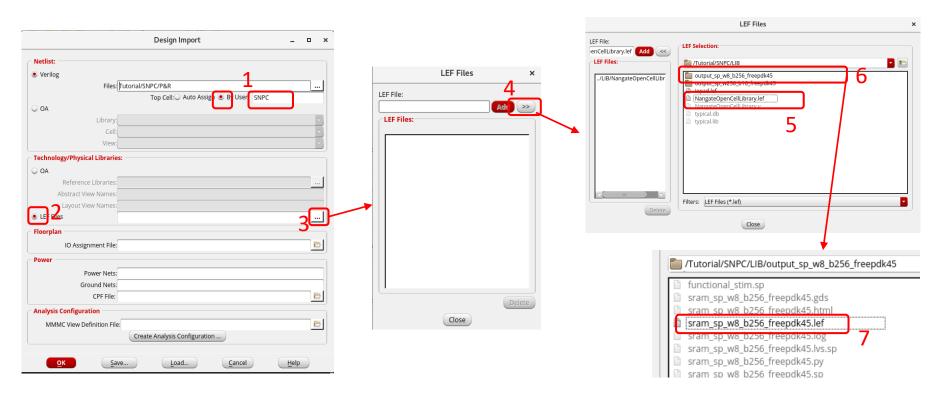

(1) In Top Cell: type SNPC. (2) Click on LEF files. (3) Click on ... to add LEF files (4) Click on >> to expand and go to ~/SNPC/LIB folder. (5) Double click on NangateOpenCellLibrary.lef and sram\_sp\_w8\_b256\_freepdk45.lef (6,7) Click Close until you get to the Design import window

### Import design- Analysis Setup (1/9)

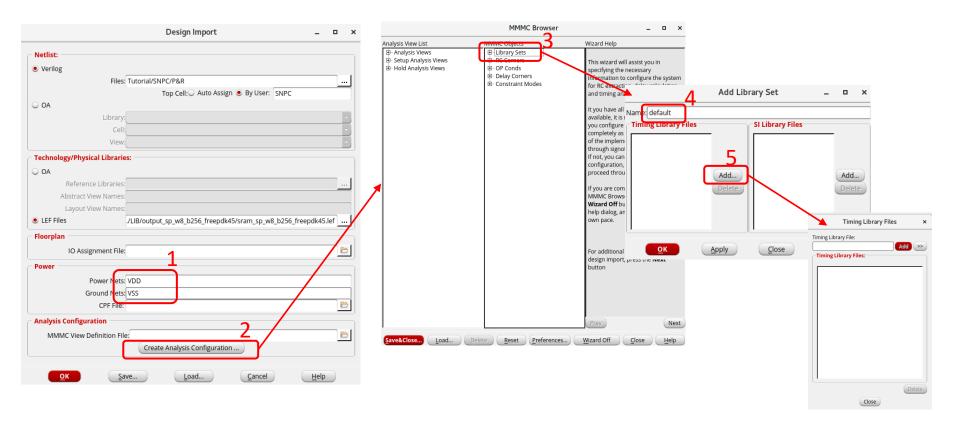

(1) Click on **Create Analysis Configuration**. (2) Double click on **Library Sets** in the **MMMC Browser window** (3) On the add *Library Set* window, type **default** in *Name* (4) Click on **Add**.

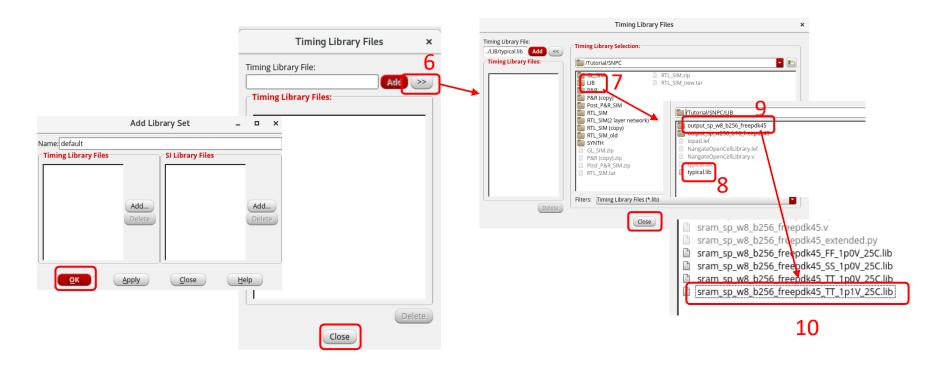

(7) In the *Timing Library* Window, go to **~/SNPC/LIB** and (8) select **typical.lib.** (9,10) select **Sram\_sp\_w8\_b256\_freepdk45\_TT\_1p1V\_25C.lib.** Click **close**(*Timing Library Files*) and then **OK**(Add *Library Set*)

# Import design- Analysis Setup (3/9)

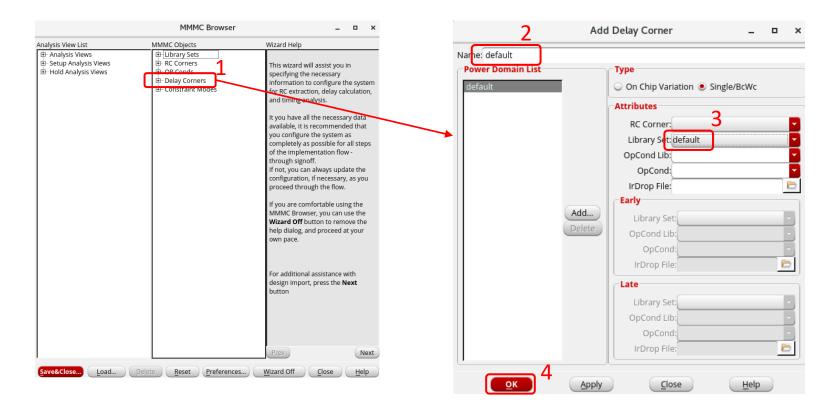

(1) Double click on **Delay Corners** in the *MMMC browser* window.

(2) On the *Add Delay Corner* window, type **default** in *Name*.

(3) Change the *Library Set* to **default**.

(4) Click **OK**

# Import design- Analysis Setup (4/9)

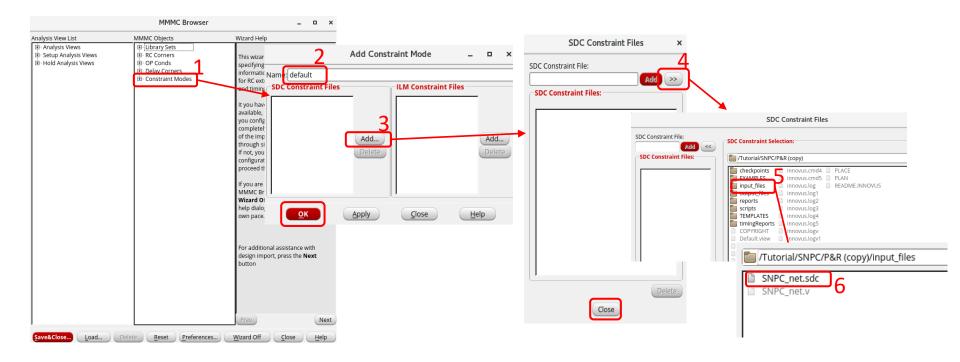

(1) Double click on *Constraint Modes* in the *MMMC browser* window. (2) On the *Add Constraint Mode* window, type **default** in *Name*. (3) Click on **Add**. (4) In the *SDC Constraint File* window, CLICK >> . (5,6) Go to ./input\_files and select SNPC\_net.sdc. Click Close(*SDC Constraint File* window) and then Ok (*Add Constraint Mode* window).

#### Import design- Analysis Setup (5/9)

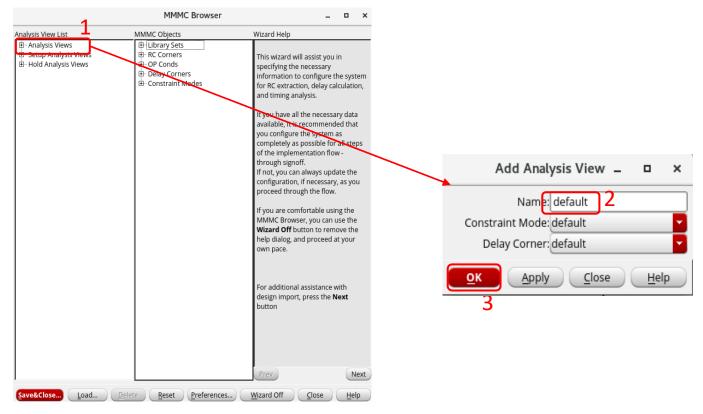

(1) Double click on Analysis Views in the MMMC browser window

(2) On the Add Analysis View window, type default in Name

(3) Click OK

# Import design- Analysis Setup (6/9)

(1) Double click on Analysis Views in the MMMC browser window

(2) On the Add Setup Analysis View window, type default in Name

(3) Click OK

## Import design- Analysis Setup (7/9)

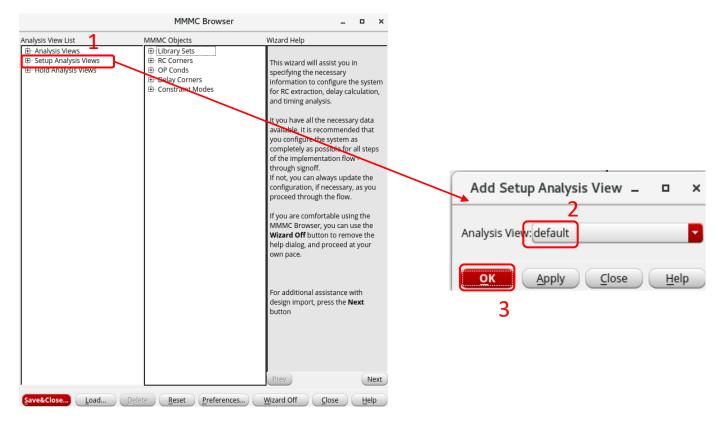

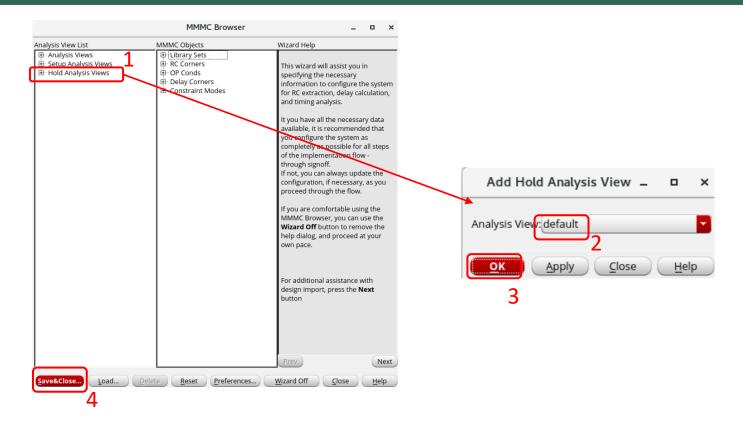

(1) Double click on Setup Analysis Views in the MMMC browser window

(2) In the Add Setup Analysis View window, make sure that Analysis View is set to default (3) Click OK. (4) Click save&close.

### Import design- Analysis Setup (8/9)

(1) Double click on **Hold Analysis Views** in the *MMMC browser* window. (2) In the *Add Hold Analysis View* Window, make sure that *Analysis View* is set to **default**. (3) Click **OK**. (4) Click on **Save&Close...** in the *MMMC browser* window. (5) Click **Save**

| Design Import _ 🗖 🗙                                                           | <u>File View Edit Partition</u> Floorplan Power <u>P</u> lace ECO <u>Clock Route Timing Verify</u> Pegasus Tools Windows Flows <u>H</u> elp | Q online help                       | cādence           |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------|

| C Netlist:                                                                    | Layout 💿                                                                                                                                    |                                     |                   |

|                                                                               | 📔 🕢 🕸 🐘 🔊 🕜 😼 🐝 🖏 🔯 🔍 🔍 🔍 🔍 🔍 🕲 👘 📰 🏔 🛆 🛈 🐝 🗞                                                                                               | 🛶 i 😁 📋 💿                           |                   |

| Verilog                                                                       | 🖳 🖯 🚸 + 🗅 👋 + 🔡 📓 🖌 🧞 🧞 🦓 🧞 🧠 🤱 🗞 🍓 1. 🔍 📖 + 🖌 + 🚔 + 🔩 🦍 🏣                                                                                  |                                     | . 🗊   📷 🗸         |

| Files: /Tutorial/SNPC/P&R                                                     |                                                                                                                                             | All Colors                          |                   |

| Top Cell: Auto Assign 💿 By User: SNPC                                         |                                                                                                                                             |                                     | V S 🛆             |

| ○ OA                                                                          |                                                                                                                                             | 🖻 Instance                          | × ×               |

| Library:                                                                      |                                                                                                                                             | Block                               | <b>× ×</b>        |

| Cell:                                                                         |                                                                                                                                             | StdCell<br>Ocover                   | <u>v</u> v<br>v v |

| View:                                                                         |                                                                                                                                             | OPhysical                           | × ×<br>× ×        |

| Technology/Physical Libraries:                                                | chefts                                                                                                                                      | OArea IO                            |                   |

|                                                                               |                                                                                                                                             | 🕀 🔘 Function                        | <b>x x</b>        |

|                                                                               | Snap TLI=68.99t                                                                                                                             | ⊞- © Status<br>⊞- Module            | × ×               |

| Reference Libraries:                                                          |                                                                                                                                             | E Cell                              |                   |

| Abstract View Names:                                                          |                                                                                                                                             | ⊞- Blockage<br>⊞- Row               | • •               |

| Layout View Names:                                                            |                                                                                                                                             | Floorplan     Forplan     Partition | • • •             |

| LEF Files     //LIB/output_sp_w8_b256_freepdk45/sram_sp_w8_b256_freepdk45.lef |                                                                                                                                             | Power                               |                   |

| r Floorplan                                                                   | A.21,R0 h, 11,R0 h, 01,R0                                                                                                                   | ⊞- Overlay<br>⊞- Track              |                   |

| IO Assignment File:                                                           |                                                                                                                                             | ⊞-Net<br>⊞-Route                    | × ×               |

|                                                                               | NEARO 1.9].RO 1.8].RO 1.6].RO 1.5].RO 1.4].RO 1.3].RO                                                                                       | 🖹 🖹 Layer                           | <b>× ×</b>        |

| Power                                                                         |                                                                                                                                             | Oactive(0)<br>Ometal1(1)            | × ×               |

| Power Nets: VDD                                                               |                                                                                                                                             | Ovia1(1)<br>Ometal2(2)              | X X X             |

| Ground Nets: VSS                                                              |                                                                                                                                             | Ovia2(2)<br>Ometal3(3)              |                   |

| CPF File:                                                                     |                                                                                                                                             | - via3(3)                           | <b>X X</b>        |

| Analysis Configuration                                                        |                                                                                                                                             | Ometal4(4)<br>Ovia4(4)              |                   |

| MMMC View Definition File:/Default.view                                       |                                                                                                                                             | Ometal5(5)<br>Ovia5(5)              | N N N             |

|                                                                               |                                                                                                                                             |                                     |                   |

| Create Analysis Configuration                                                 |                                                                                                                                             | Ovia6(6)<br>Ometal7(7)              | × ×               |

|                                                                               |                                                                                                                                             | Detail ()                           | Sneed             |

| OK Save Load Cancel Help                                                      |                                                                                                                                             |                                     |                   |

|                                                                               | Q Click to select single object. Shift+Click to de/select multiple objects.                                                                 | 3.21250, 395.73750 Sel: 0           | In Memory         |

(1) Click Ok

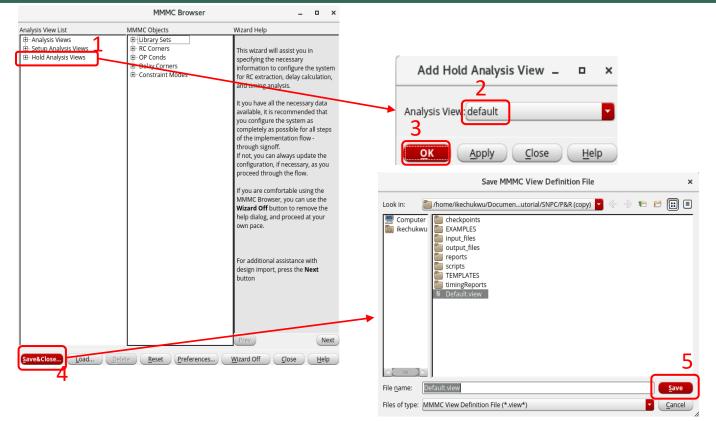

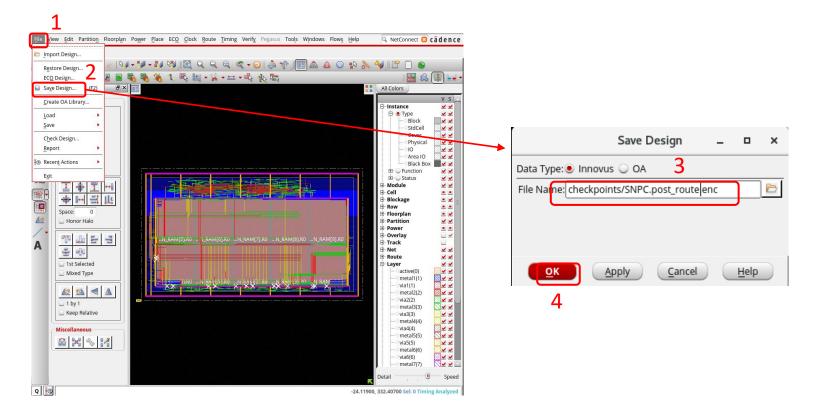

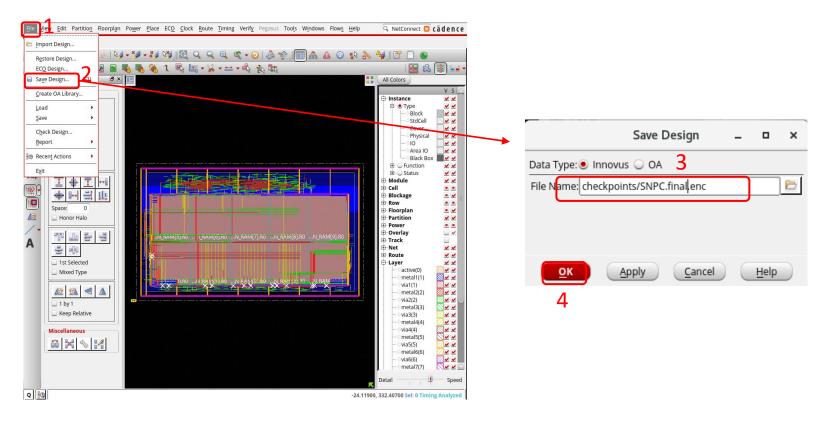

#### Import Design- Checkpoint

In the welcome screen, we can see the modules of SNPC before placement. We should save the progress at each step. (1) Click File-> (2) Save Design (3) Check Innovus (4) Click on the folder icon. (5) Select the checkpoints folder (6) Save file as import.enc (7) Save and click OK

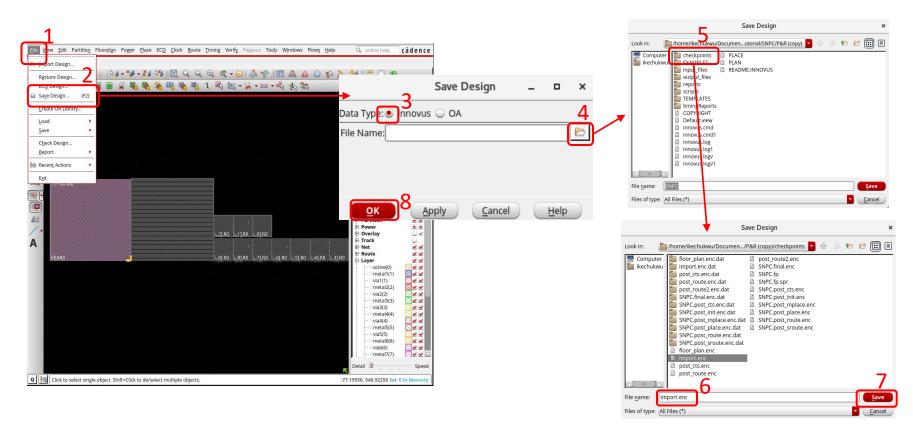

#### **Step 2: Specify Floorplan**

(1) In this step we specify the floorplan Click Floorplan-> (2) Specify Floorplan. (3)

Check Die Size by. (4) Enter 370 for Width and 220 Height. (5) Enter 15 for • Core to

Left • Core to Right • Core to Top • Core to Bottom. (6) Click OK

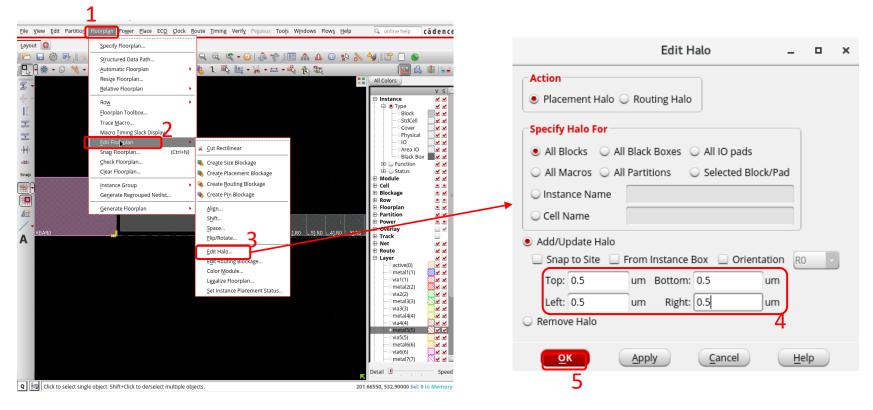

#### Step 3: Add Halo to Block

(1) In this step we specify the floorplan Click **Floorplan**->. (2) **Edit Floorplan. (**3) Click **Edit Halo** (4) Enter 0.5 for •**Top** • **Bottom** •**Left** •**Right. (**5) Click **OK**

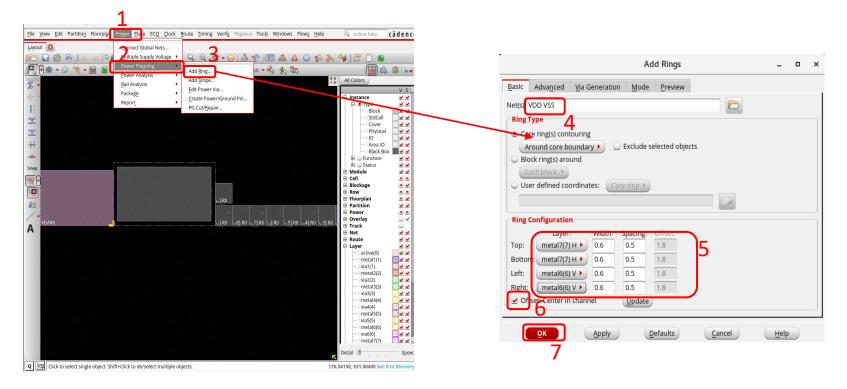

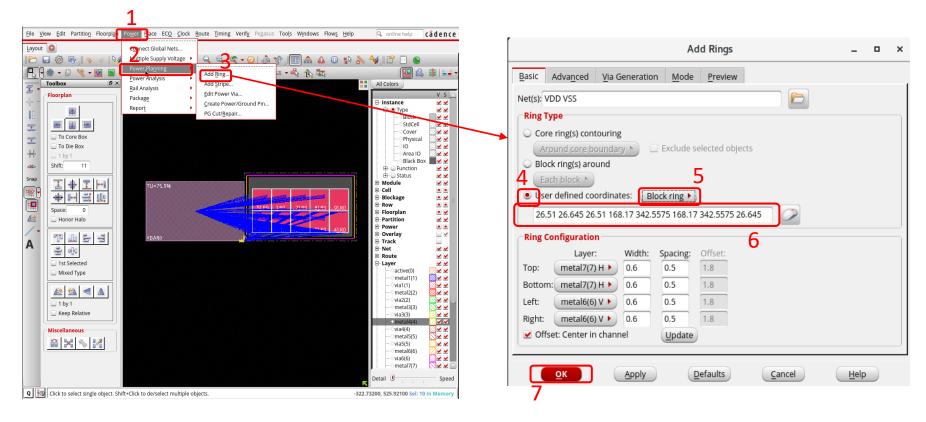

#### Step 4: Add Core Rings

(1) In this step we specify the floorplan Click Power-> (2)Select Power Planning. (3)

Click Add Rings (4) Select VDD VSS. (5) Select metal7H for • Top and • Bottom (Layer), select metal6V for • LEFT and • Right (Layer). Enter 0.6 for Width and 0.5 for Spacing.

(6) Check Offset Center in Channel (7) Click OK

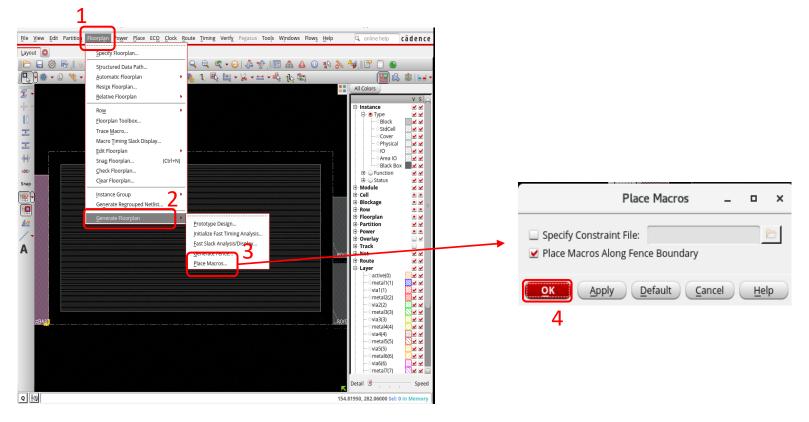

#### Step 5: Place Macro (1/2)

(1) Click on Floorplan (2) Select Generate floorplan. (3) Click on Place Macro.(4) Click OK

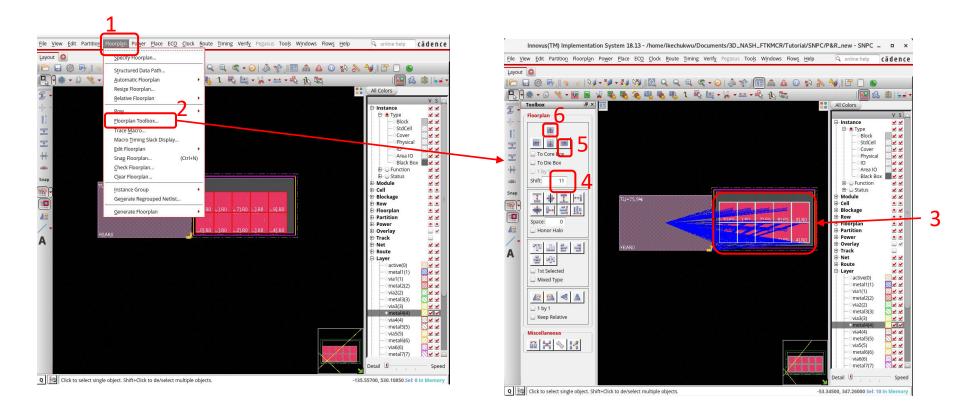

#### Step 5: Place Macro (2/2)

(1) Click on **Floorplan.** (2) Select **Floor Plan Toolbox**. (3) Select the SRAM macros by holding Ctrl and left clicking on them. (4) Set the **Shift** value to 11. (5) Click on the right arrow, and (6) the up arrow to shift once in each direction

#### Step 6: Add Block Rings

(1) In this step we specify the floorplan Click Power-> (2)Select Power Planning. (3) Click Add Rings (4) Select User defined coordinates. (5) Select Block ring. (6) Enter the values 26.51 26.645 26.51 168.17 342.5575 168.17 342.5575 26.245 for the clock ring coordinates. (7) Click OK

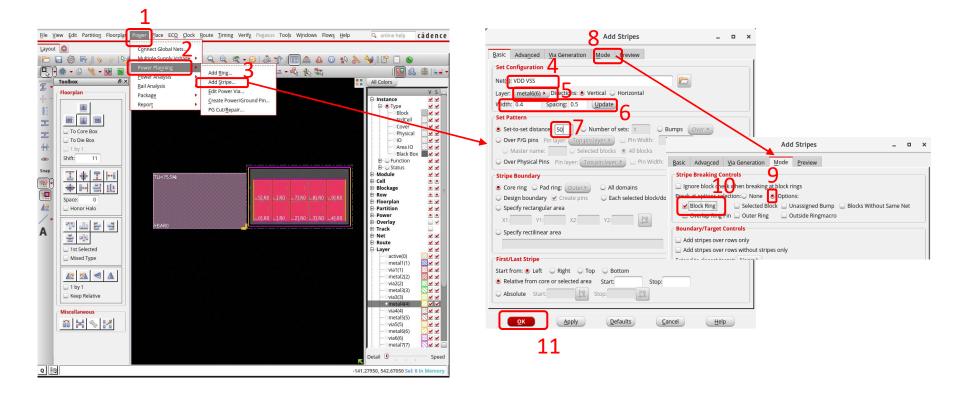

#### Step 7: Add Power Stripe

(1) Click on Power-> (2) Power Planning-> (3)Add Stripe. (4) Input VDD VSS in Nets(s): (5)

Change Layer to metal 6, (6) Set: • Width to 0.4 • Spacing to 0.5, (7) Change Set-to-setdistance to 50. (8) Click on Mode. (9) Check Options. (10) Check Block Rings. (11) Click OK

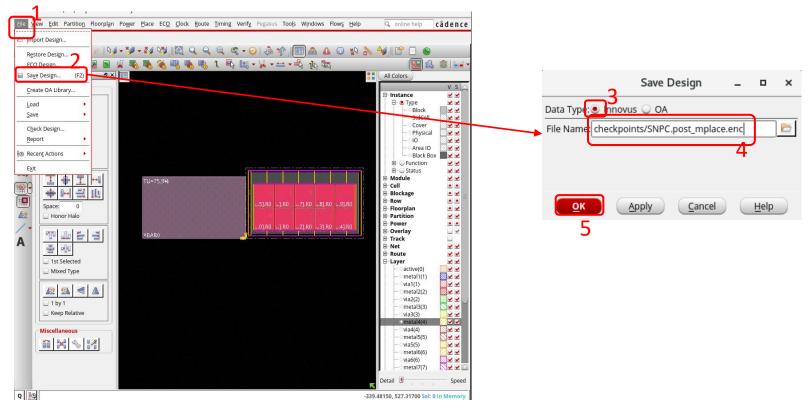

#### Save Design Progress- Checkpoint

In the welcome screen, we can see the floorplan and the placed macros. Save the progress. (1) Click File-> (2) Click on Save Design (3) select Innovus. (4) Enter the checkpoints directory, and save the design progress as SNPC.post\_mplace.enc. (5) Click on OK

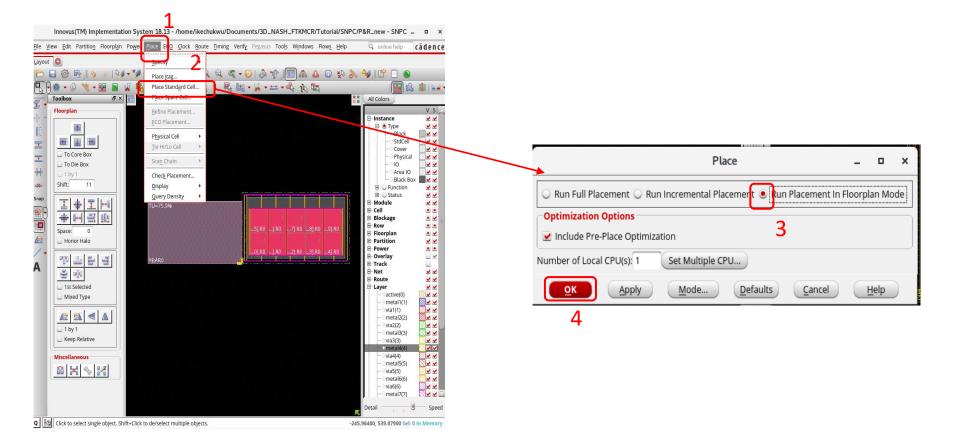

#### Step 8: Place Standard Cell

Now we place the SNPC modules on the die: (1) Click Place-> (2) Place Standard Cell. (3) select Run Placement in Floorplan Mode. (4) Click OK

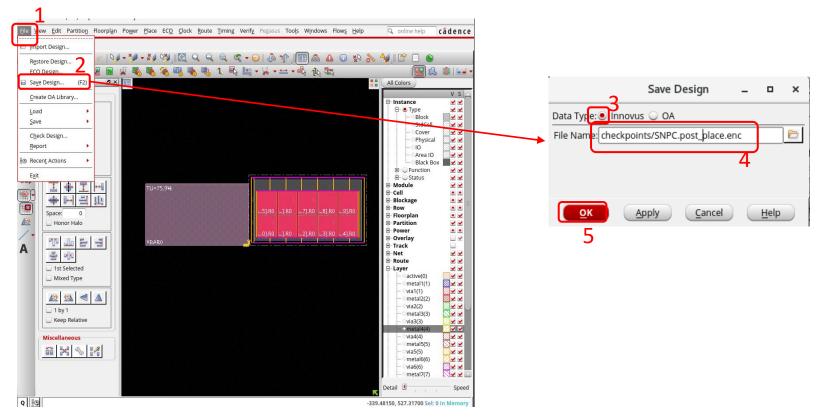

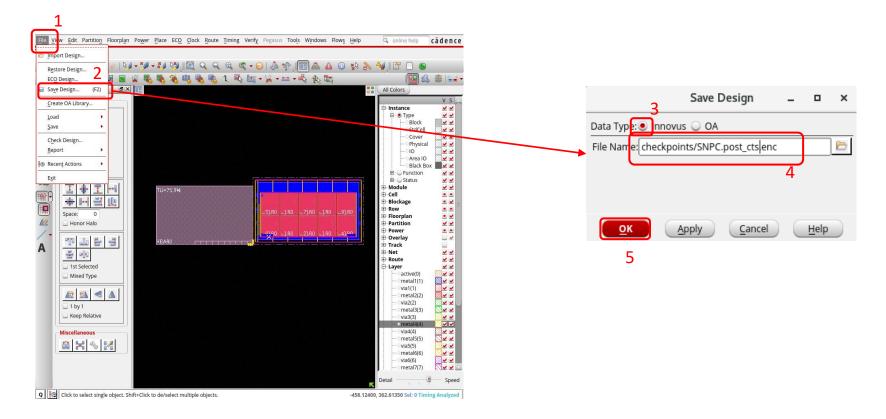

## Save Design Progress- Checkpoint

In the welcome screen, we can see the floorplan and the placed macros. Save the progress. (1) Click File-> (2) Click on Save Design (3) select Innovus. (4) Enter the checkpoints directory, and save the design progress as SNPC.post\_place.enc. (5) Click on OK

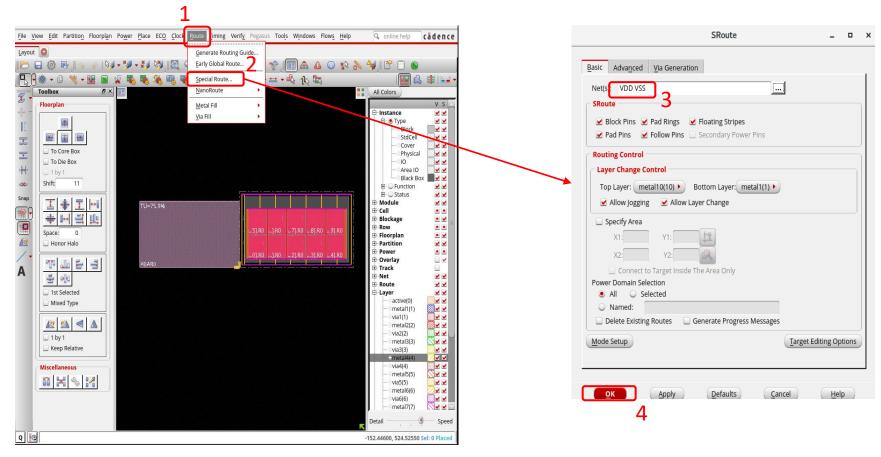

#### **Step 9: Power Routing**

(1) Click on Route-> (2) Special Route. (3) Input VDD VSS in Nets(s): (4) Click OK

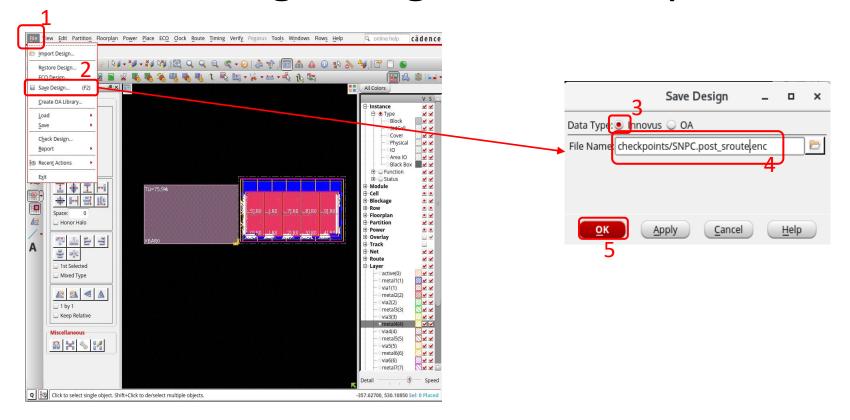

#### Save Design Progress- Checkpoint

In the welcome screen, we can see the floorplan and the placed macros. Save the progress. (1) Click File-> (2) Click on Save Design (3) select Innovus. (4) Enter the checkpoints directory, and save the design progress as SNPC.post\_sroute.enc. (5) Click on OK

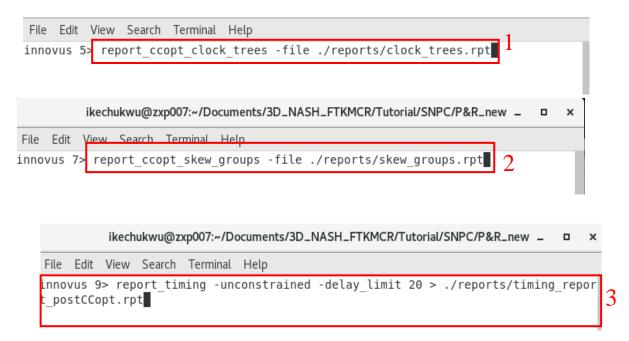

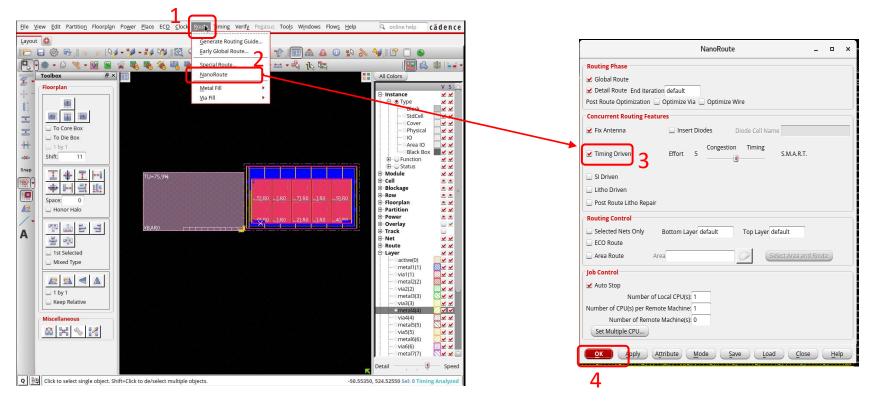

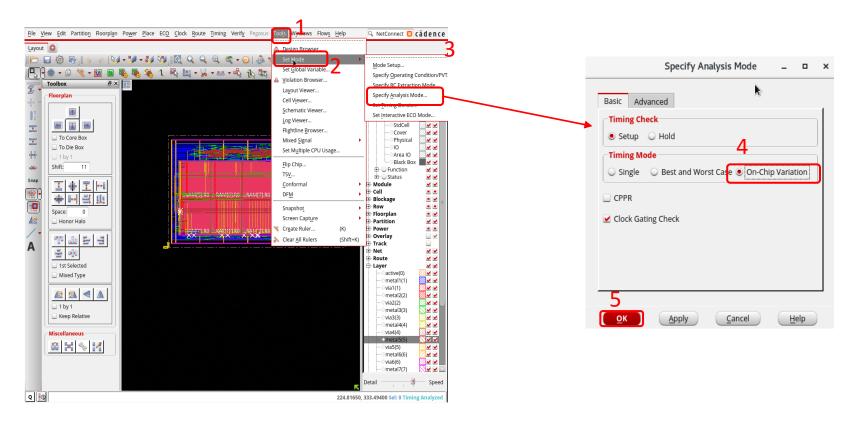

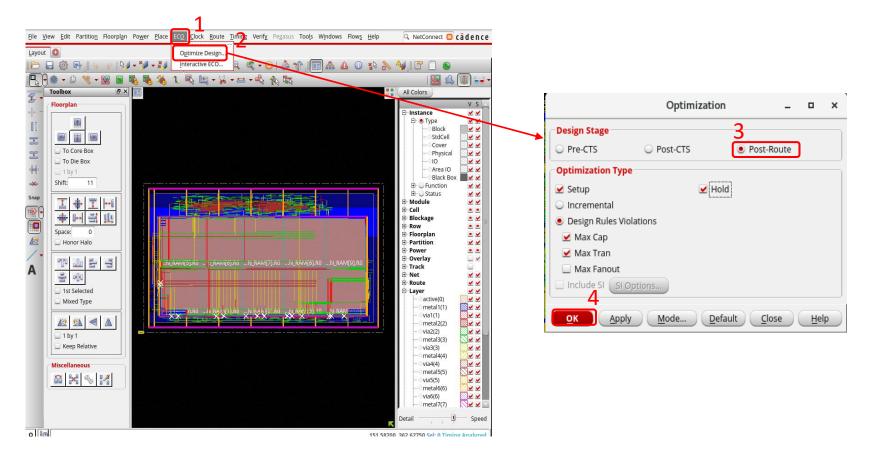

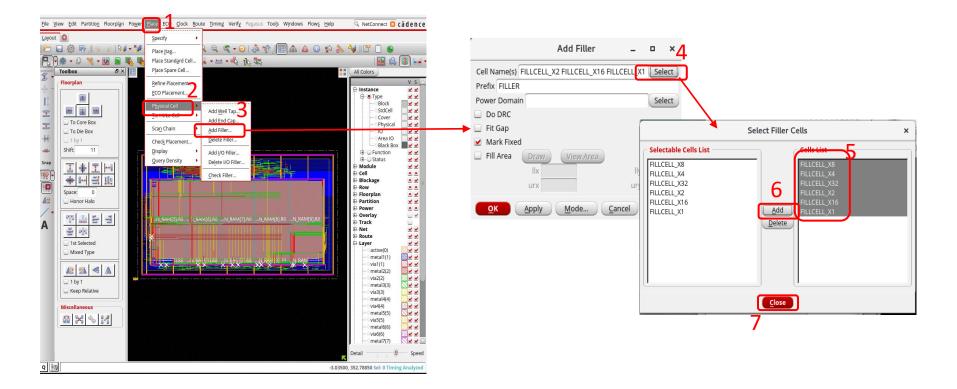

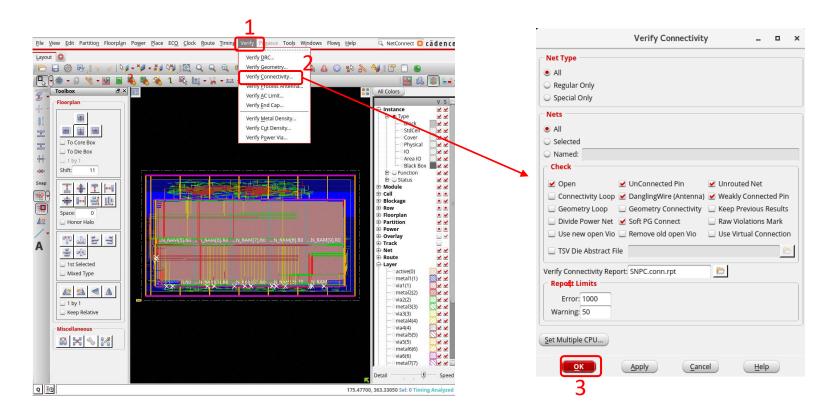

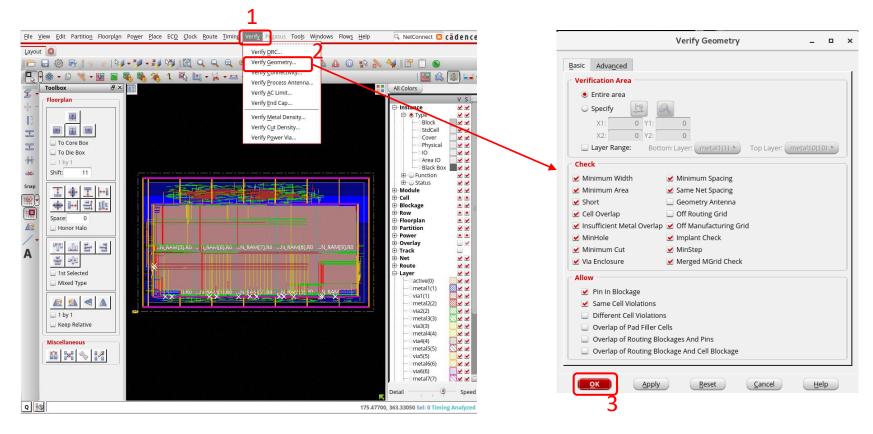

### Step 10: Clock Tree Synthesis