1. Introduction

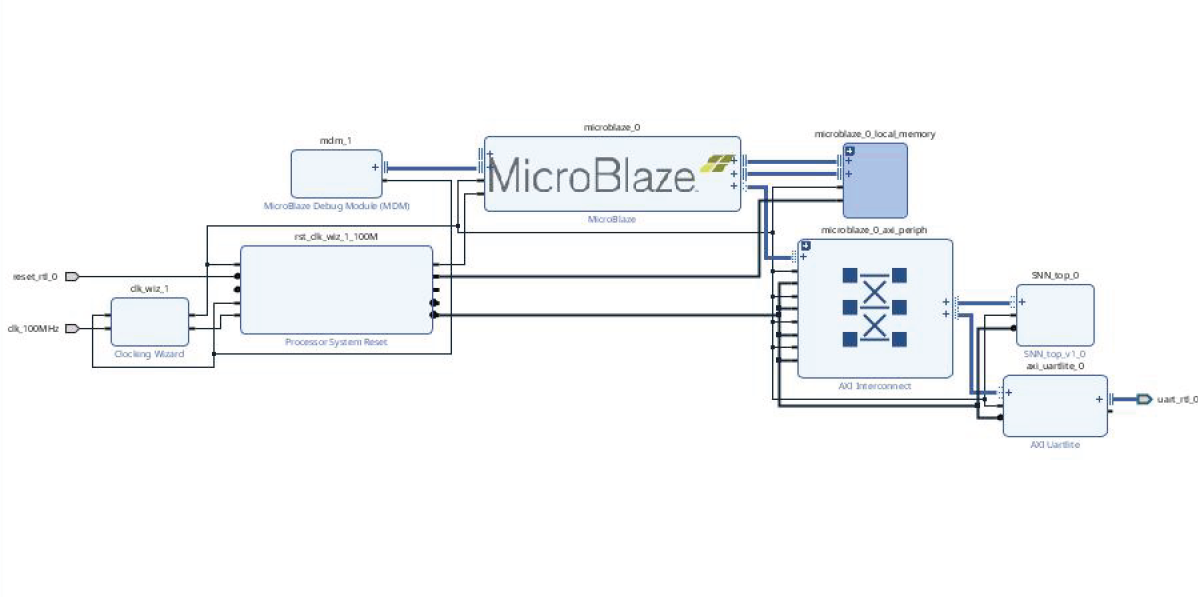

The DN-SOC (Digital Neuron System on Chip) project is designed for implementing Spiking Neural Networks (SNN) using a Xilinx FPGA platform. This project aims to create a highly efficient and scalable SNN IP core that can be integrated into larger systems for neuromorphic computing applications.

The DN-SOC FPGA design provides a flexible platform to model and simulate SNNs, with support for high-speed processing, low power consumption, and adaptability to various hardware configurations. The project leverages Xilinx's powerful FPGA resources to deliver real-time processing capabilities for SNN-based applications.

This implementation is optimized for Xilinx FPGAs and includes a pre-designed SNN IP core that can be customized for different use cases. Modifications are required for those who wish to adapt the design for specific FPGA configurations or for ASIC implementations.

2. Design Tutorial

-

Download the Zip File:

- Click on DN-SOC Xilinx FPGA Project to download the zip file containing the SNN IP core and other necessary source code.

- Save the file to a location on your computer where you can easily access it.

-

Extract the Zip File:

- Navigate to the location where you saved the zip file.

- Right-click on the file and select "Extract All" to unzip the contents.

-

Explore the Xilinx FPGA Code:

- Open your Xilinx development environment (such as Xilinx Vivado or Vitis).

- Import the extracted source files into your Vivado project.

-

Customize the SNN IP Core:

- Modify the IP core parameters according to your hardware requirements (e.g., clock speed, number of neurons, etc.).

- Adjust the design for power efficiency, timing constraints, and other FPGA-specific optimizations.

-

Compile and Run the Code:

- For Xilinx FPGA: Compile the Verilog or VHDL code and synthesize it for your specific FPGA device.

- Run the simulation or implementation as required by your project.

- For testing: Deploy the compiled design onto a Xilinx FPGA and observe the SNN processing behavior on hardware.