1. Introduction

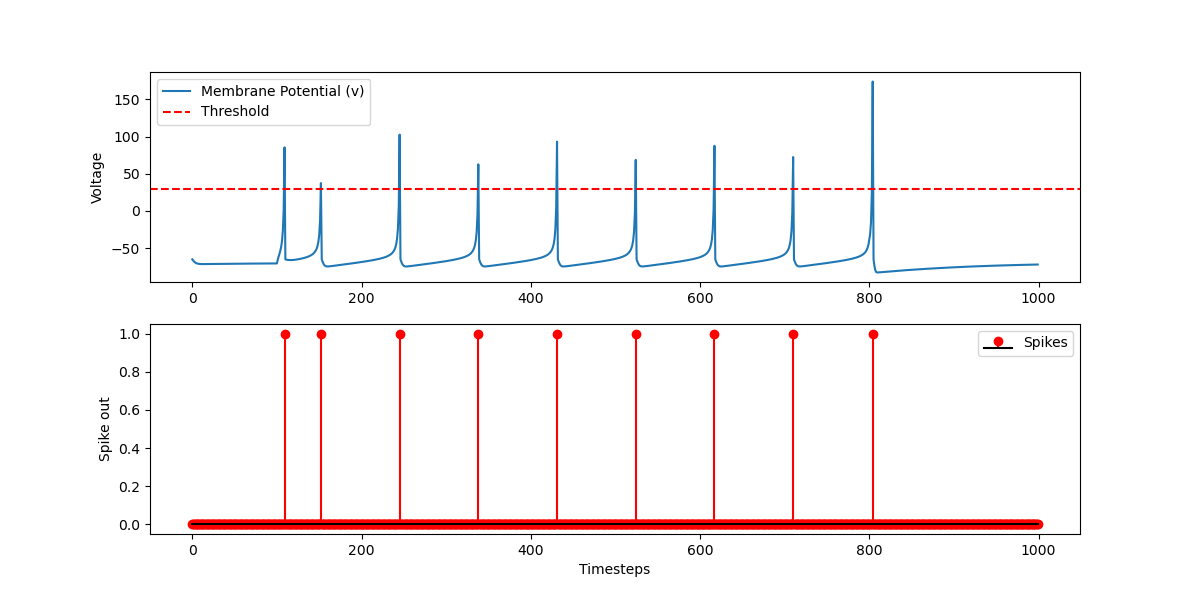

The Izhikevich neuron model is a widely used spiking neuron model that balances biological accuracy with computational efficiency. It captures the firing dynamics of neurons using a simple mathematical representation, making it suitable for simulating large-scale spiking neural networks.

This tutorial provides both Python code for simulating the Izhikevich neuron and Verilog HDL code for hardware implementation. These resources enable the integration of spiking neural networks into software simulations and hardware designs, facilitating research and development in neuromorphic computing.

The Verilog HDL implementation provided here is based on a single clock cycle design, which is ideal for simulation and testing. However, modifications are needed for those who intend to implement these neurons on FPGA or ASIC hardware, where more complex timing and synchronization might be required.

2. Design Tutorial

-

Download the Zip File:

- Click on Izhikevich Neuron Design to download the zip file containing Python and Verilog source code.

- Save the file to a location on your computer where you can easily access it.

-

Extract the Zip File:

- Navigate to the location where you saved the zip file.

- Right-click on the file and select "Extract All" to unzip the contents.

-

Run the Python Code:

- Ensure you have Python installed on your system (preferably Python 3.x).

- Open the provided Python script in your favorite IDE or text editor.

- Run the script to simulate the spiking behavior of the Izhikevich neuron and visualize the output.

-

Open the Verilog Source Code:

- Open your Verilog development environment (such as ModelSim, Xilinx Vivado, or another Verilog-compatible IDE).

- Import the extracted Verilog source files into your project.

-

Compile and Run the Verilog Code:

- Compile the Verilog source code within your development environment.

- Run the simulation or synthesis as required by your project.