1. Introduction

Spike-Timing Dependent Plasticity (STDP) is a biological learning mechanism that adjusts synaptic weights based on the relative timing of pre- and post-synaptic spikes. It is critical for implementing on-chip learning in spiking neural networks.

This tutorial focuses on the implementation of STDP learning in Leaky Integrate-and-Fire (LIF) neurons. The LIF neuron models biological neuron behavior with a "leak" mechanism that reduces accumulated potential over time, making it ideal for realistic neuromorphic systems.

The implementation includes both Verilog HDL for hardware realization and Python for prototyping and simulation.

The Verilog HDL implementation provided here is based on a single clock cycle design, which is ideal for simulation and testing. However, modifications are needed for those who intend to implement these neurons on FPGA or ASIC hardware, where more complex timing and synchronization might be required.

2. Design Tutorial

-

Download the Project Files:

- Click on STDP for LIF Neurons to download the zip file containing Verilog and Python source code.

- Save the file to a location on your computer where you can easily access it.

-

Extract the Files:

- Navigate to the location where you saved the zip file.

- Right-click on the file and select "Extract All" to unzip the contents.

-

Run the Python Code:

- Open a Python development environment (such as Jupyter Notebook, PyCharm, or VS Code).

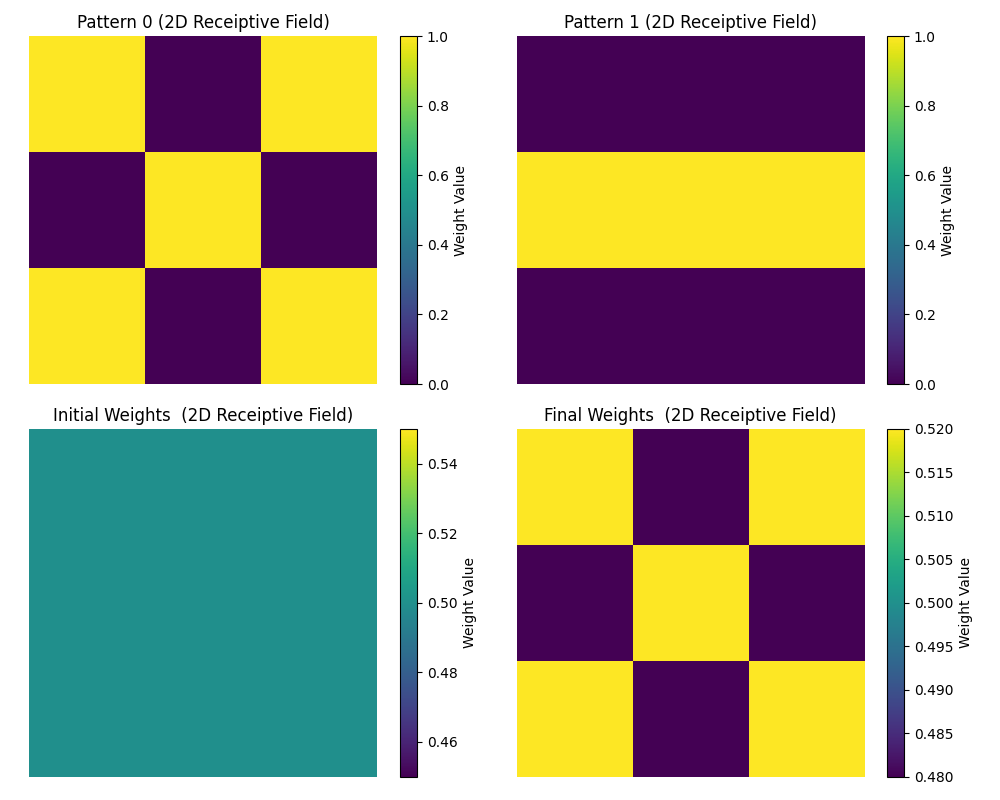

- Run the provided Python script to simulate the STDP learning process in LIF neurons.

- Visualize weight updates and spiking behavior through plots generated by the script.

-

Open the Verilog Code:

- Use a Verilog development environment (such as ModelSim, Xilinx Vivado, or another Verilog-compatible IDE).

- Import the Verilog files for STDP and LIF neuron designs into your project.

-

Simulate the Verilog Design:

- Compile the Verilog source code within your development environment.

- Run simulations to observe spike behavior and weight adjustments based on STDP rules.