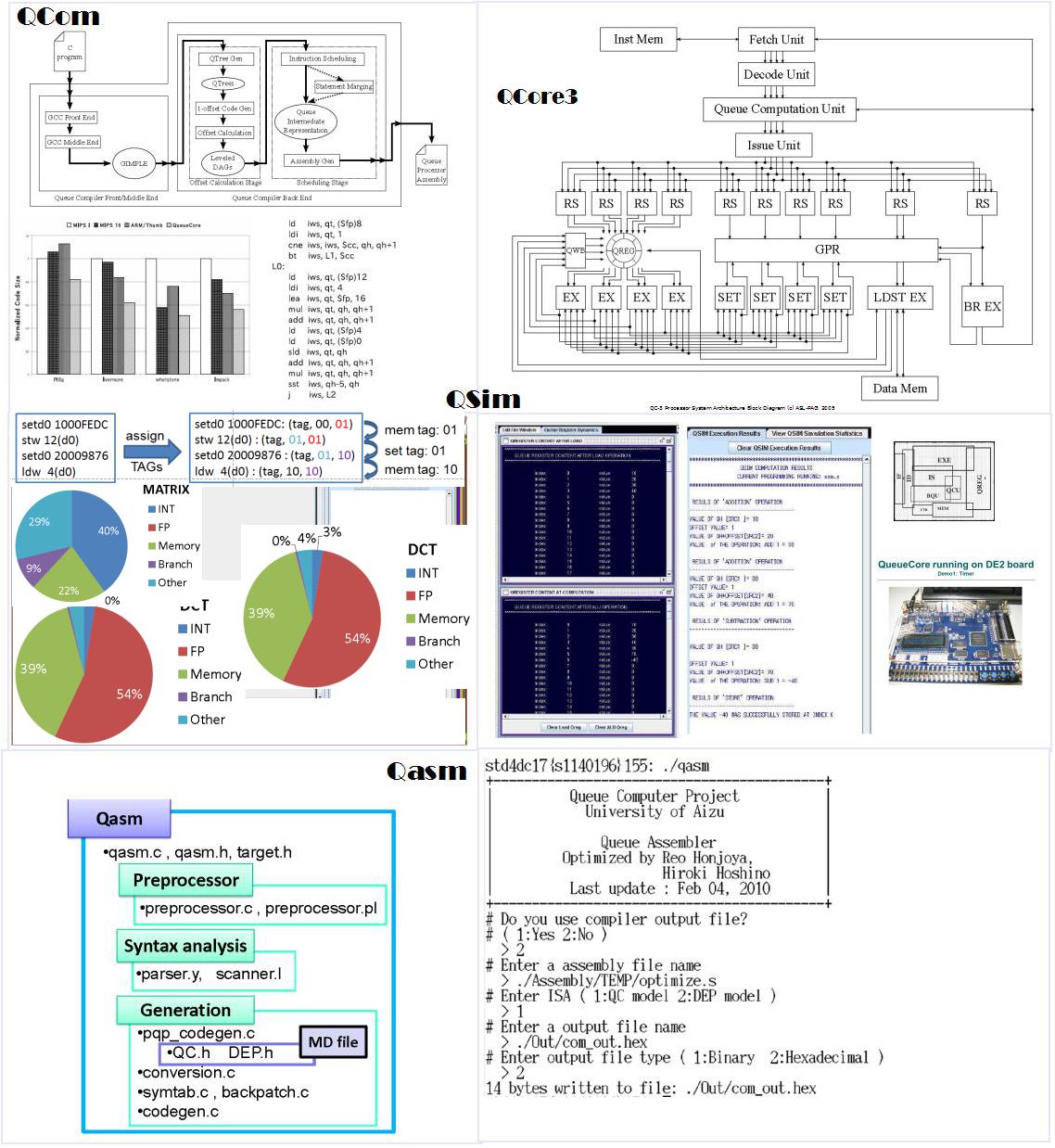

The complete developed tool-chain is made of

compiler (QCom), assembler(Qasm), functional and cycle accurate

simulator (QSim), and soft-core hardware processor (QueueCore

(QC-1, QC-2, and QC-3)). Note: Your use of any information or

materials on this website is entirely at your own risk, for

which we shall not be liable.

(c) Ben Abdallah Abderazek, 1999-2009.