1. Overview

This tutorial provides a step-by-step guide to the physical design of the Spiking Neuron Processing Core (SNPC) using Verilog HDL, Cadence tools, and Modelsim. It covers the complete flow from RTL simulation to synthesis, place and route (P&R), and post-layout verification.

2. Design Phases

- Specification and RTL Design: Develop Verilog HDL code for 256 LIF neurons, synapse memory, and STDP learning logic.

- RTL Simulation: Use Modelsim to simulate testbenches for functionality verification.

- Synthesis: Use Cadence Genus to generate a gate-level netlist with the Nangate open cell library.

- Place and Route: Perform layout generation using Cadence Innovus.

- Post-Layout Verification: Verify timing and connectivity using extracted layouts.

3. Key Steps

- Environment Setup:

- Source the Cadence setup script:

source ~/.cad.sh. - Launch the appropriate tool (e.g.,

modelsim,genus, orinnovus).

- Source the Cadence setup script:

- RTL Simulation:

- Navigate to the simulation directory:

~/SNPC/RTL_SIM/work/. - Run the Modelsim script:

do ../script/run_Local_MNIST.tcl.

- Navigate to the simulation directory:

- Synthesis:

- Navigate to the synthesis directory:

~/SNPC/SYNTH/. - Run the synthesis script:

source script/snpc.tcl.

- Navigate to the synthesis directory:

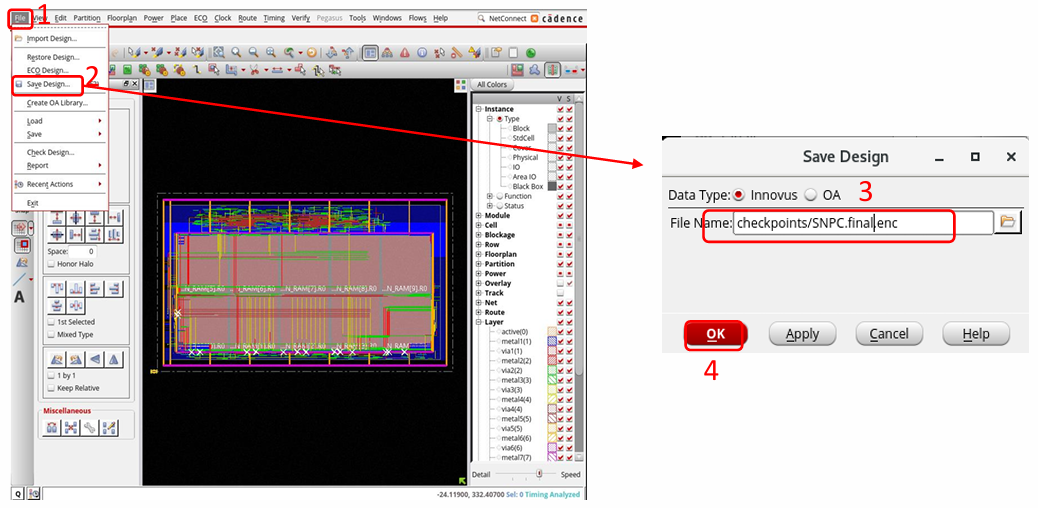

- Place and Route:

- Navigate to the P&R directory:

~/SNPC/PnR/. - Run the P&R script:

source scripts/SNPC.tcl.

- Navigate to the P&R directory:

4. Tools and Resources

- Tools: Modelsim, Cadence Genus, Cadence Innovus.

- Libraries: Nangate open cell library, SRAM libraries.

- Dataset: MNIST dataset converted to spikes using Poisson distribution.

For detailed documentation, download the full tutorial: SNPC Physical Design (PDF).