Advanced On-chip Interconnects and 3D-ICs

Principal Investigators: Abderazek Ben Abdallah (PI), Khanh N. Dang (PI)

Our research addresses the key challenges of this transition by exploring advanced on‑chip interconnects and 3D‑IC technologies, including 3D chiplets, 2.5D/3D packaging, hybrid bonding, and photonic‑electronic interconnects. We investigate scalable and energy‑efficient 3D NoCs, AI accelerators with stacked memory, and reliability‑driven design methodologies to ensure robust operation in deep 3D stacks.

This work tackles critical issues such as fault

tolerance, TSV‑based vertical integration, photonic

communication, low‑power mapping, adaptive routing,

and emerging reliability challenges

inherent to next‑generation heterogeneous many‑core

systems.

- Patent

No. 7488989: A three-dimensional system on

chip in which a TSV group connects between layers

(2024).

Inventors: Abderazek Ben Abdallah, Khanh N. Dang

[View Patent Details] - Patent

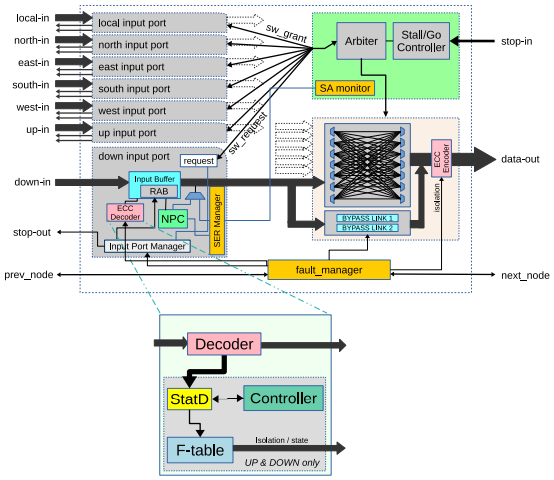

No. 7239099: TSV Error Tolerant Router

Device for 3D Network On Chip (2023).

Inventors: Abderazek Ben Abdallah, Khanh N. Dang, Masayuki Hisada

[View Patent Details] - Patent

No. 6846027: Defect tolerance router for

network on-chip (2021).

Inventors: Abderazek Ben Abdallah

[View Patent Details] - Patent

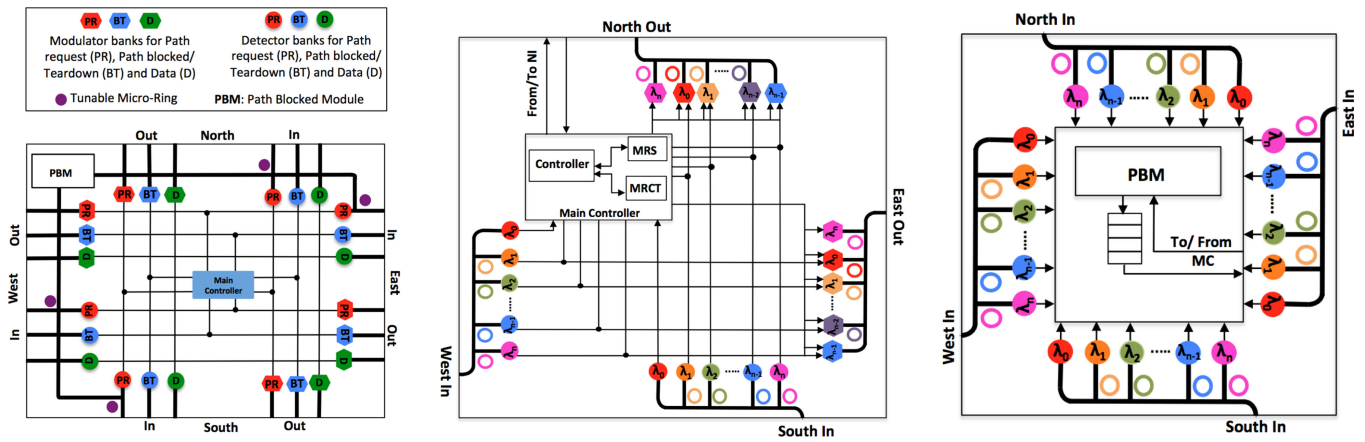

No. 6747660: Optical network-on-chip system

using non-block photo-switches (2020).

Inventors: Abderazek Ben Abdallah

[View Patent Details] - Patent

No. 6284177: Error resilience router and

control method (2018).

Inventors: Abderazek Ben Abdallah

[View Patent Details]

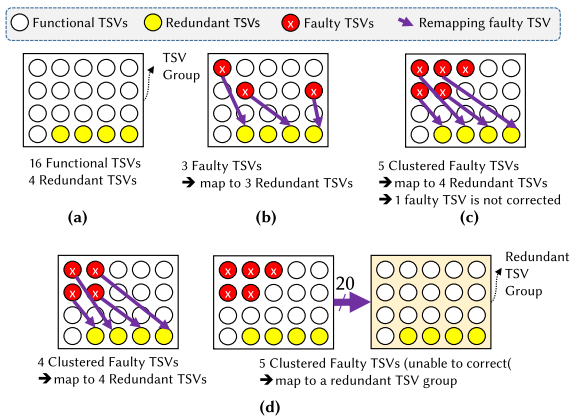

- K. N. Dang, A. B. Ahmed, A. B. Abdallah and X. -T. Tran, "HotCluster: A Thermal-Aware Defect Recovery Method for Through-Silicon-Vias Toward Reliable 3-D ICs Systems," in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 41, no. 4, pp. 799-812, April 2022

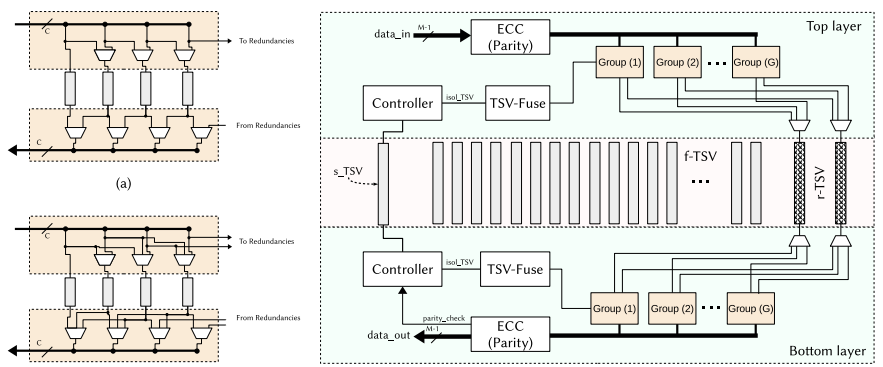

- K. N. Dang, M. C. Meyer, A. B. Ahmed, A. B. Abdallah and X. -T. Tran, "A Non-Blocking Non-Degrading Multiple Defects Link Testing Method for 3D-Networks-on-Chip," in IEEE Access, vol. 8, pp. 59571-59589, 2020

- The H. Vu, Yuichi Okuyama, Abderazek Ben Abdallah, “Comprehensive Analytic Performance Assessment and K-means based Multicast Routing Algorithms and Architecture for 3D-NoC of Spiking Neurons,” ACM Journal on Emerging Technologies in Computing Systems (JETC)

- T. H. Vu, O. M. Ikechukwu and A. Ben Abdallah, "Fault-Tolerant Spike Routing Algorithm and Architecture for Three Dimensional NoC-Based Neuromorphic Systems," in IEEE Access, vol. 7, pp. 90436-90452, 2019

- K. N. Dang, A. B. Ahmed, A. B. Abdallah and X. -T. Tran, "A Thermal-Aware On-Line Fault Tolerance Method for TSV Lifetime Reliability in 3D-NoC Systems," in IEEE Access, vol. 8, pp. 166642-166657, 2020

- Wang, Jiangkun, Ogbodo Mark Ikechukwu, Khanh N. Dang, and Abderazek Ben Abdallah, "Spike-Event X-ray Image Classification for 3D-NoC-Based Neuromorphic Pneumonia Detection," Electronics 11, no. 24: 4157

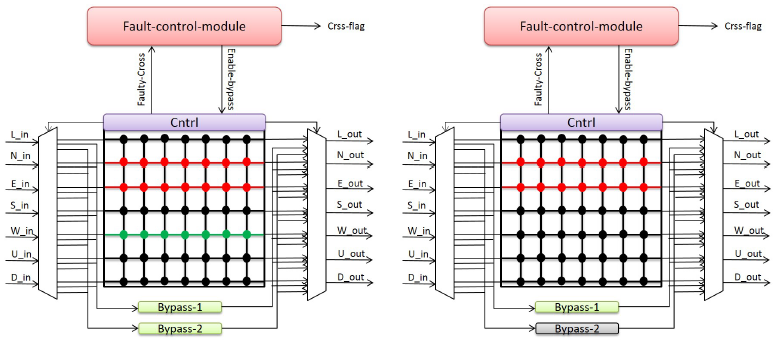

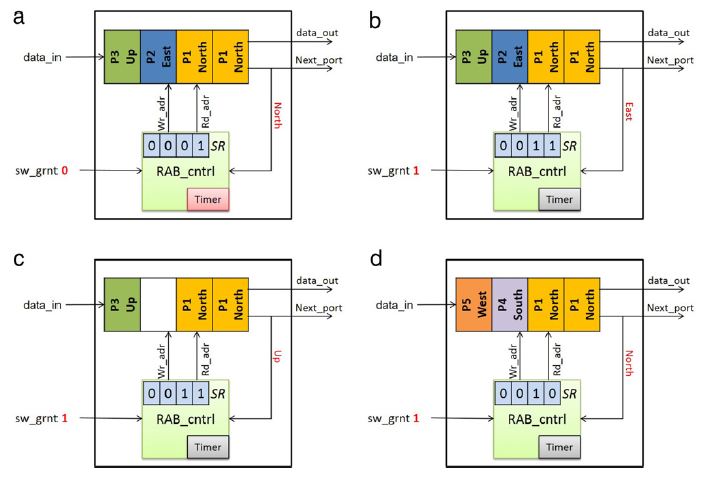

- Khanh N. Dang, Michael Meyer, Yuichi Okuyama, Abderazek Ben Abdallah, "A Low-overhead Soft-Hard Fault Tolerant Architecture, Design and Management Scheme for Reliable High-performance Many-core 3D-NoC Systems,” Journal of Supercomputing (2017) 73:2705–2729.

- Akram Ben Ahmed, A. Ben Abdallah, "Architecture and Design of High-throughput, Low-latency and Fault-Tolerant Routing Algorithm for 3D-Network-on-Chip,” The Journal of Supercomputing, December 2013, Volume 66, Issue 3, pp 1507-1532.

- Akram Ben Ahmed, A. Ben Abdallah, "Architecture and Design of Real-Time Systems for Elderly Health Monitoring," Journal of Embedded Systems, 2017, Vol.9, No.5, pp.484 – 494.

- Akram Ben Ahmed, Abderazek Ben Abdallah, "Adaptive Fault-Tolerant Architecture and Routing Algorithm for Reliable Many-Core 3D-NoC Systems", Journal of Parallel and Distributed Computing, Volumes 93–94, July 2016, Pages 30-43.

- Akram Ben Ahmed, A. Ben Abdallah,”Graceful Deadlock-Free Fault-Tolerant Routing Algorithm for 3D Network-on-Chip Architectures,” Vournal of Parallel and Distributed Computing, 74/4 (2014), pp. 2229-2240.

- Abderazek Ben Abdallah, M. Masuda, A. Canedo, K. Kuroda, “Natural Instruction Level Parallelism-aware Compiler for High-Performance QueueCore Processor Architecture,” The Journal of Supercomputing, Volume 57, Number 3, pp. 314-338, Sept. 2011.

- Akram Ben Ahmed, T. Ouchi, S. Miura, A. Ben Abdallah, “Run-Time Monitoring Mechanism for Efficient Design of Application-specific NoC Architectures in Multi/Manycore Era,” Proc. IEEE 6th International Workshop on Engineering Parallel and Multicore Systems (ePaMuS2013′), July 2013.

- Akram Ben Ahmed, A. Ben Abdallah, “ONoC-SPL Customized Network-on-Chip (NoC) Architecture and Prototyping for Data-intensive Computation Applications,” IEEE Proceedings of The 4th International Conference on Awareness Science and Technology, pp. 257-262, 2012.

- A. Ben Ahmed, A. Ben Abdallah, K. Kuroda, “Architecture and Design of Efficient 3D Network-on-Chip (3D NoC) for Custom Multicore SoCs,” IEEE Proc. of the 5th International Conference on Broadband, Wireless Computing, Communication and Applications (BWCCA-2010), Nov. 2010.

- K. Mori, A. Esch, A. Ben Abdallah, K. Kuroda, “Advanced Design Issues for OASIS Network-on-Chip Architecture,” IEEE Proc. of the 5th International Conference on Broadband, Wireless Computing, Communication and Applications (BWCCA-2010), Nov. 2010, pp. 74-79.

Collaborations & Contact

We collaborate with the following

companies:

- STARG, Inc.

- Aizu Computer Science Laboratories, Inc.

- Banpu Japan K.K. (BJP), a subsidiary of Banpu NEXT

Co., Ltd.

Contact: Abderazek Ben Abdallah (E-mail: benab@u-aizu.ac.jp)