Neuromorphic Computing and Brain-Inspired Systems

Principal Investigators: Abderazek Ben Abdallah (PI), Khanh N. Dang (PI)

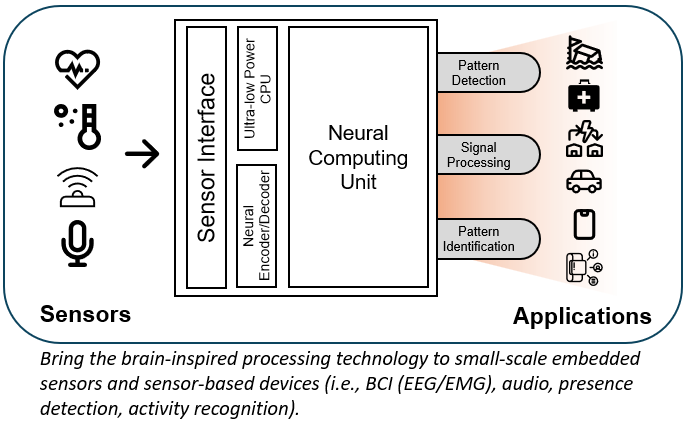

NASH: Neuromorphic Adaptive System Hardware

We are pioneering the development of the NASH chip, an ultra-low-power processing unit designed for real-time cognitive tasks. This research focuses on the integration of 3D Network-on-Chip (NoC) interconnects to overcome the data-movement bottlenecks of conventional 2D architectures. By utilizing adaptive configuration methods, the NASH system allows for on-the-fly adjustment of Spiking Neural Network (SNN) parameters, including synaptic weights and neuronal thresholds. This flexibility enables the hardware to self-optimize for diverse biological signals, bringing high-performance brain-inspired processing to edge-level BCI devices.

ApproxiMorph: Energy-Efficient AI Co-Design

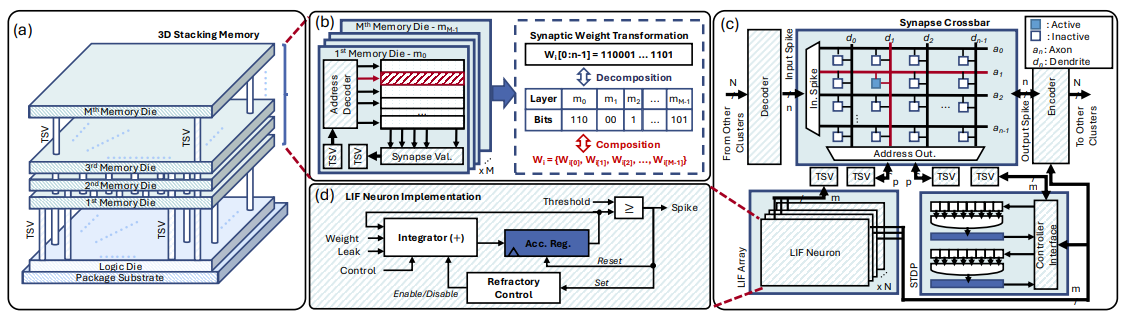

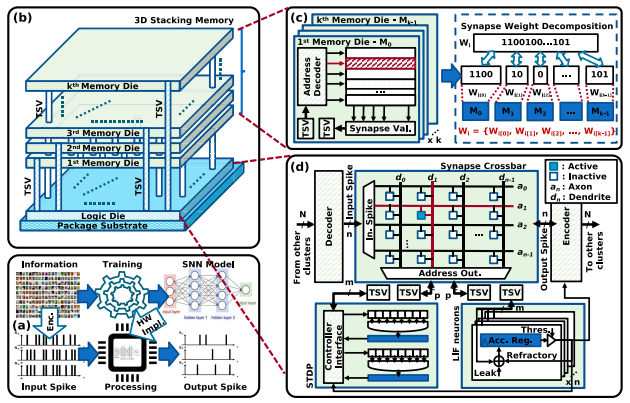

ApproxiMorph exploits the inherent noise resilience of Spiking Neural Networks by implementing layer-wise approximation strategies within 3D-stacked IC designs. The framework integrates approximate neuron designs with low-voltage 3D-stacked SRAM to significantly reduce the power-per-synaptic operation. By utilizing a heuristic search algorithm to navigate a massive configuration space (over 1017 options), the system identifies optimal mappings that achieve nearly 30% power reduction with almost no impact on classification performance.

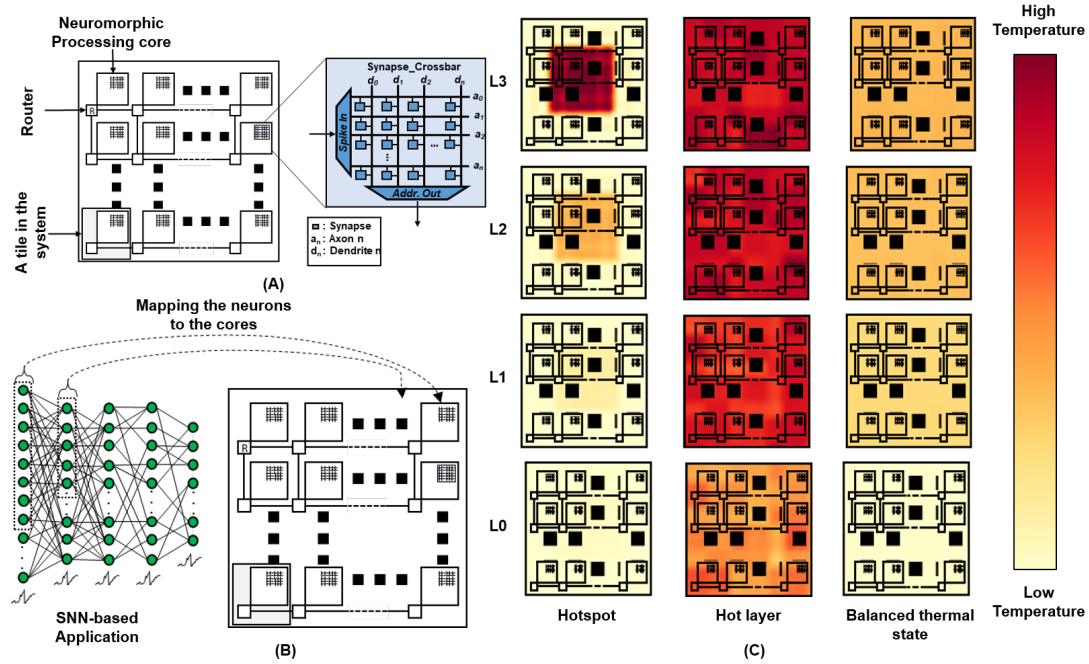

BTSAM: Balanced Thermal-State-Aware Mapping

The BTSAM framework introduces a periodic activity scoring system to monitor the workload of 3D-NoC nodes. By applying Seesaw Neuron Clustering (SNC) and a thermal-aware genetic algorithm, the system dynamically redistributes neuronal tasks to eliminate hot spots. This proactive thermal management prevents structural damage and results in a 5K peak temperature reduction and a four-fold increase in Mean-Time-to-Failure (MTTF).

Partial Voltage Scaling in 3D Stacking Synaptic Memory

This research tackles the "memory wall" by decoupling synaptic weight storage from processing elements through vertical stacking. By splitting synaptic weights into significant and least-significant subsets across different 3D layers, the system can independently control the supply voltage. This allows for power-gating of memory layers containing less critical data, achieving SOP energy reductions of up to 66%.

R-MaS3N: Robust Fault-Tolerant Mapping

R-MaS3N is a mapping framework designed to maintain system integrity in the presence of physical manufacturing defects. When a hardware fault is detected, R-MaS3N facilitates rapid remapping of SNN layers to functional neuronal clusters. The system maintains 100% efficiency even when 40% of hardware nodes are faulty, reducing remapping time by 71 times compared to conventional methods.

Registered and Provisional Patents

- [Patent No. 7699791] (June 20, 2025) - Abderazek Ben Abdallah, Hoang Huang Kun, Dang Nam Khanh, Song Janning, "AI Processor" [Source]

- [Patent No. 7277682] (May 11, 2023) - Abderazek Ben Abdallah, The H. Vu, Masayuki Hisada, "Spiking Neural Network by 3D NoC" [Google Patents]

- Neural Network Processor (Provisional 2024-047372) - Khanh N. Dang, Abderazek Ben Abdallah, Nguyen Ngo Doanh

Selected Publications

- Ryoji Kobayashi, Ngo-Doanh Nguyen, Abderazek Ben Abdallah, Nguyen Anh Vu Doan and Khanh N. Dang, "ApproxiMorph: Energy-efficient Neuromorphic System with Layer-wise Approximation of Spiking Neural Networks and 3D-Stacked SRAM", in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, doi: 10.1109/TCAD.2025.3597251.

- N. -D. Nguyen, K. N. Dang, A. B. Ahmed, A. Ben Abdallah and X. -T. Tran, "NOMA: A Novel Reliability Improvement Methodology for 3-D IC-based Neuromorphic Systems," in IEEE Transactions on Components, Packaging and Manufacturing Technology, doi: 10.1109/TCPMT.2024.3488113.

- M. Maatar, Z. Wang, K. N. Dang and A. Ben Abdallah, "BTSAM: Balanced Thermal-State-Aware Mapping Algorithms and Architecture for 3D-NoC-Based Neuromorphic Systems," in IEEE Access, vol. 12, pp. 126679-126692, 2024, doi: 10.1109/ACCESS.2024.3425900.

- K. N. Dang, N. A. V. Doan, N. -D. Nguyen and A. Ben Abdallah, "HeterGenMap: An Evolutionary Mapping Framework for Heterogeneous NoC-Based Neuromorphic Systems," in IEEE Access, vol. 11, pp. 144095-144112, 2023, doi: 10.1109/ACCESS.2023.3345168.

- N. -D. Nguyen, A. B. Ahmed, A. Ben Abdallah and K. N. Dang, "Power-Aware Neuromorphic Architecture With Partial Voltage Scaling 3-D Stacking Synaptic Memory," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 31, no. 12, pp. 2016-2029, Dec. 2023, doi: 10.1109/TVLSI.2023.3318231.

- W. Y. Yerima, K. N. Dang and A. Ben Abdallah, "R-MaS3N: Robust Mapping of Spiking Neural Networks to 3D-NoC-Based Neuromorphic Systems for Enhanced Reliability," in IEEE Access, vol. 11, pp. 94664-94678, 2023, doi: 10.1109/ACCESS.2023.3311031.

- N. -D. Nguyen, X. -T. Tran, A. Ben. Abdallah and K. N. Dang, "An In-Situ Dynamic Quantization With 3D Stacking Synaptic Memory for Power-Aware Neuromorphic Architecture," in IEEE Access, vol. 11, pp. 82377-82389, 2023, doi: 10.1109/ACCESS.2023.3301560.

- O. M. Ikechukwu, K. N. Dang and A. B. Abdallah, "On the Design of a Fault-Tolerant Scalable Three Dimensional NoC-Based Digital Neuromorphic System With On-Chip Learning," in IEEE Access, vol. 9, pp. 64331-64345, 2021

- K. N. Dang, A. B. Ahmed, A. B. Abdallah and X. -T. Tran, "TSV-OCT: A Scalable Online Multiple-TSV Defects Localization for Real-Time 3-D-IC Systems," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 28, no. 3, pp. 672-685, March 2020

- Ben Abdallah A, Dang KN. Toward Robust Cognitive 3D Brain-Inspired Cross-Paradigm System. Front Neurosci. 2021 Jun 25;15:690208. doi: 10.3389/fnins.2021.690208.

- Ogbodo Mark Ikechukwu, Khanh N. Dang and Abderazek Ben Abdallah, "Energy-efficient Spike-based Scalable Architecture for Next-generation Cognitive AI Computing Systems," Springer Lecture Note in Computer Science (LNCS), International Symposium on Ubiquitous Networking 2021 (UNET21), May 19 ? May 22, 2021, Marakesh, Morocco (Best Student Paper Award).

- The H. Vu, Yuichi Okuyama, Abderazek Ben Abdallah, "Analytical performance assessment and high-throughput low-latency spike routing algorithm for spiking neural network systems," Journal of Supercomputing 75, pp. 5367?5397 (2019)

- Ogbodo Mark Ikechukwu, Khanh N. Dang, Tomohide Fukuchi, Abderazek Ben Abdallah, "Architecture and Design of a Spiking Neuron Processor Core Towards the Design of a Large-scale Event-Driven 3D-NoC-based Neuromorphic Processor," ACM Chapter International Conference on Educational Technology, Language and Technical Communication (ETLTC), January 27-31, 2020, Aizuwakamatsu, Japan.

- Mark Ogbodo, The Vu, Khanh N. Dang and Abderazek Abdallah, "Light-weight Spiking Neuron Processing Core for Large-scale 3D-NoC based Spiking Neural Network Processing Systems," The 7th IEEE International Conference on Big Data and Smart Computing, February 19-22, 2020, Pusan, South Korea.

- Khanh N. Dang and Abderazek Ben Abdallah "An Efficient Software-Hardware Design Framework for Spiking Neural Network Systems," 2019 IEEE International Conference on Internet of Things, Embedded Systems and Communications (IINTEC 2019), Tunis, Tunisia, 2019, pp. 155-162.

- The H. Vu, Abderazek Ben Abdallah, "A Low-latency K-means based Multicast Routing Algorithm and Architecture for Three Dimensional Spiking Neuromorphic Chips," IEEE International Conference on Big Data and Smart Computing (BigComp 2019), Kyoto, Japan, February 28 - March 2, 2019 (Best Paper Award).